DMA control device and image processor

A control unit, one-way technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problem of accurate and reasonable judgment of multiple requests of image function modules

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

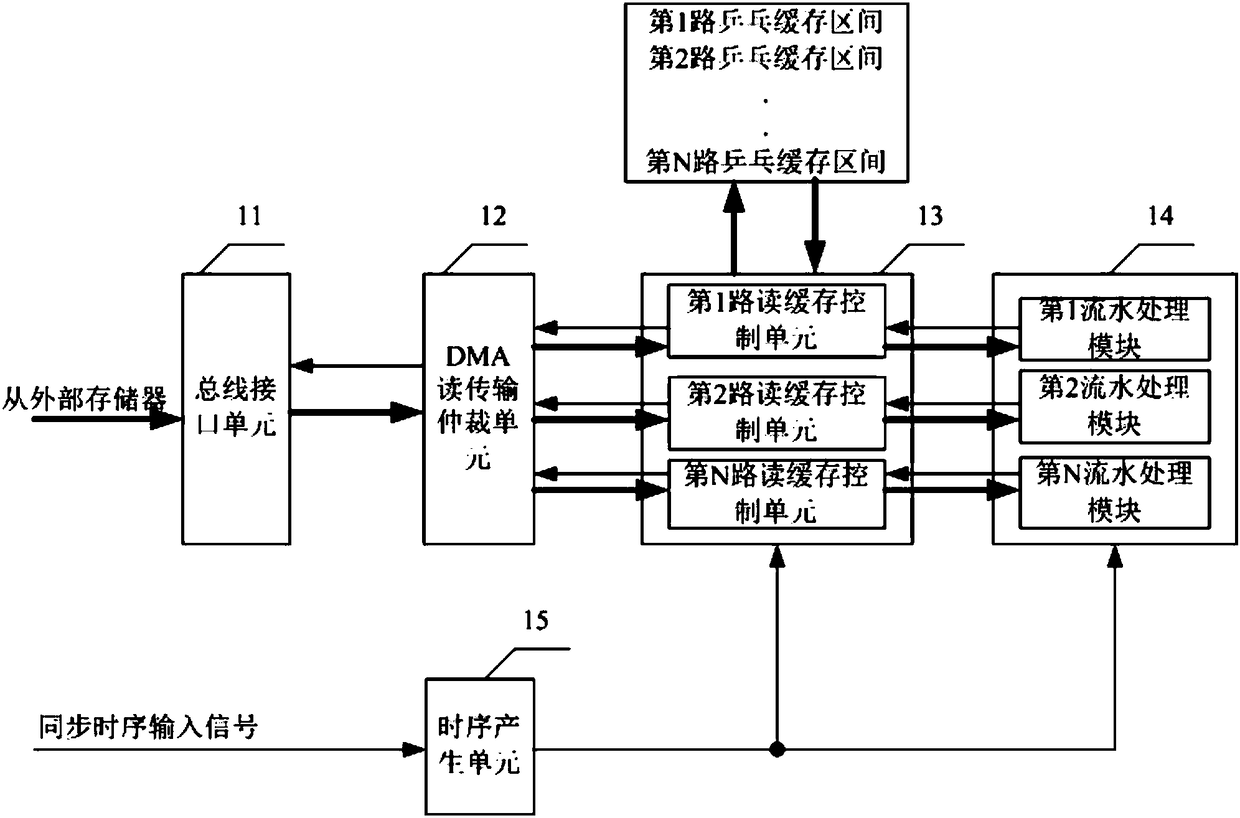

[0035] see figure 1 The DMA control device provided by Embodiment 1 of the present invention includes a bus interface unit 11, a DMA read transfer arbitration unit 12, an N-way read cache control unit 13, N pipeline processing modules 14, and a timing generation unit 15, wherein N is greater than or It is a natural number equal to 2, and the number of N depends on the number of pipeline processing modules in the image processor and the number of modules that need to access the external frame buffer.

[0036] The bus interface unit 11 is used to receive the read request signal and the transfer information generated by the DMA read transfer arbitration unit 12, and convert the read request signal and the transfer information into a bus request signal of a composite system bus protocol (such as an AXI bus, etc.). After receiving valid data on the bus, write the read buffer data read from the external memory to the DMA read transfer arbitration unit 12;

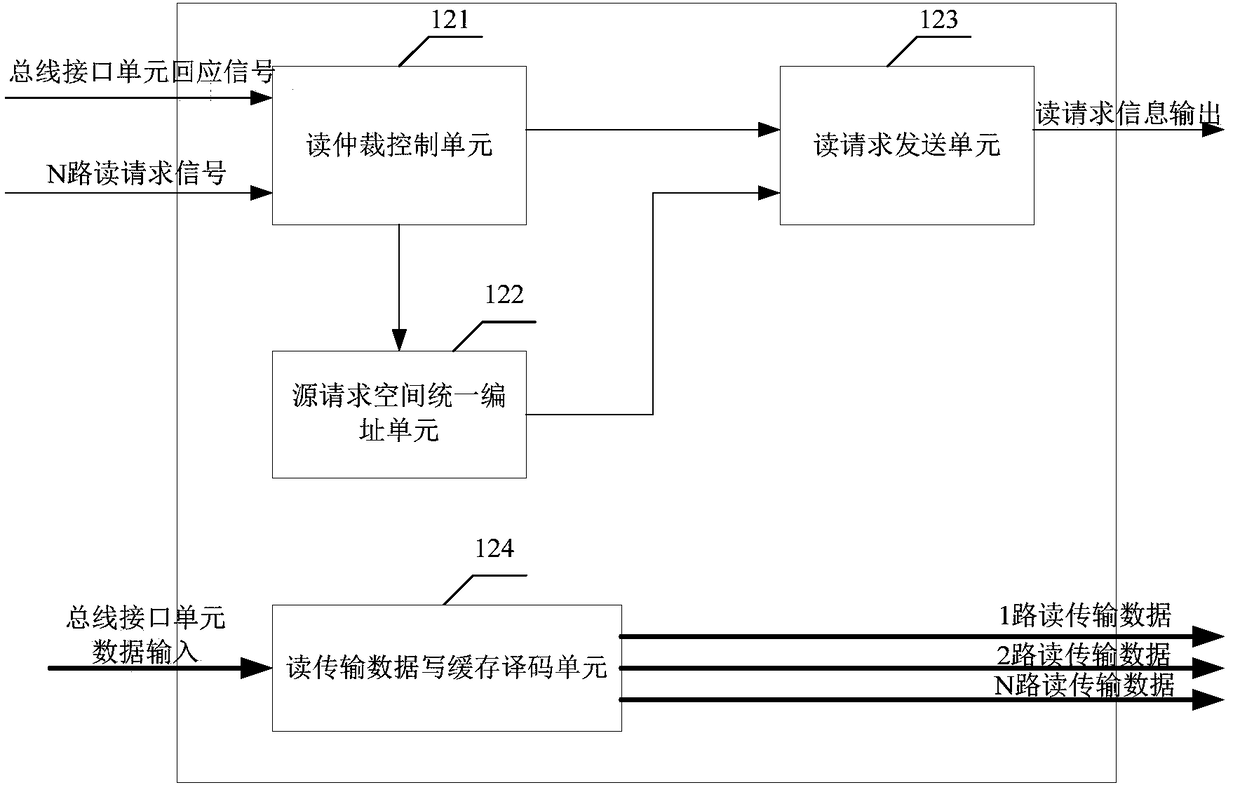

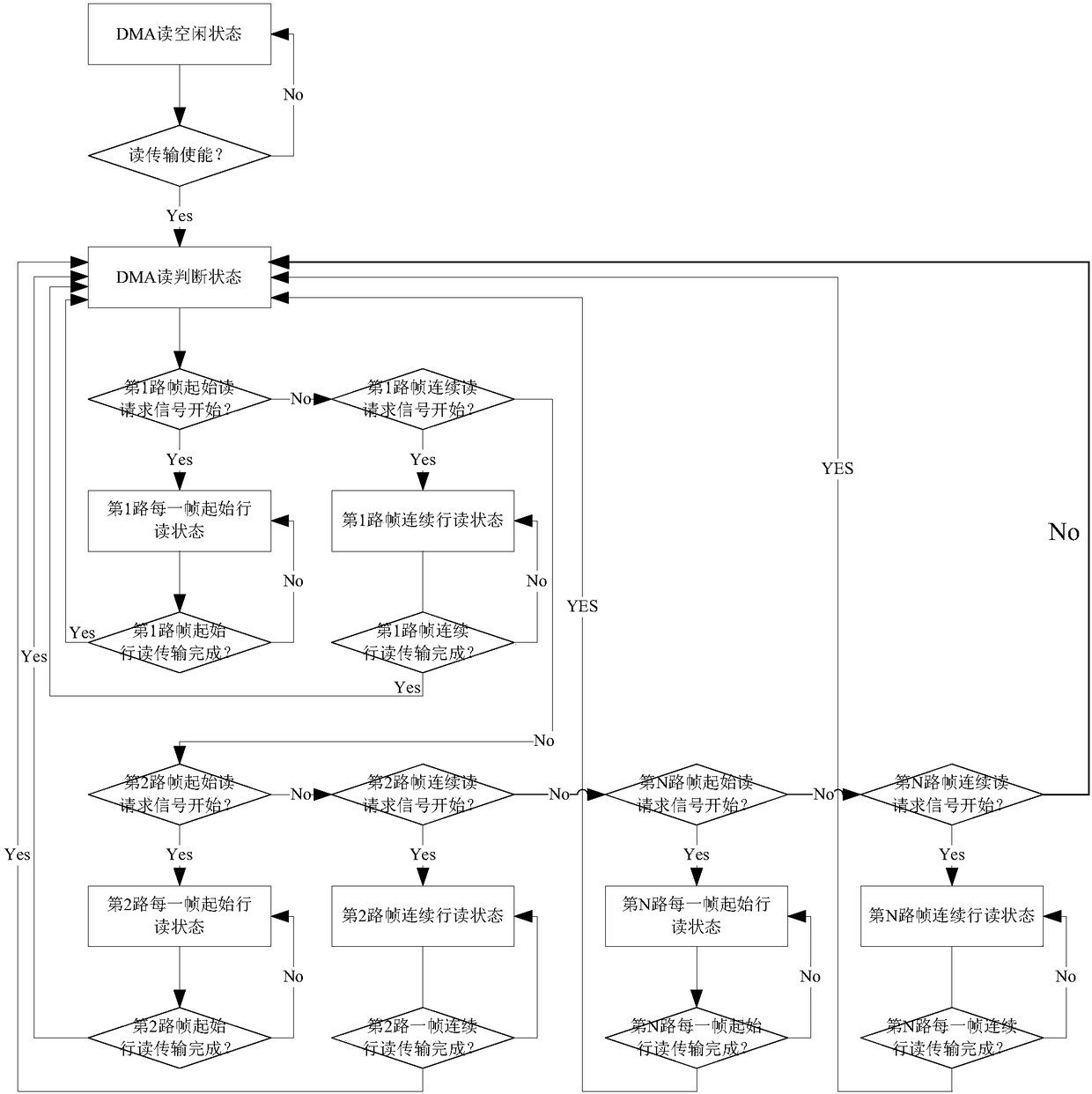

[0037] The DMA read tran...

Embodiment 2

[0063] see Figure 5 The difference between the DMA control device provided in Embodiment 2 of the present invention and the DMA control device provided in Embodiment 1 of the present invention is that the DMA control device provided in Embodiment 2 of the present invention further includes a DMA write transfer arbitration unit 22 and an N-way write buffer control Unit 23.

[0064] The bus interface unit is also used to receive the write request signal and the transfer information generated by the DMA write transfer arbitration unit 22, and convert the write request signal and the transfer information into a bus request signal of a composite system bus protocol (such as an AXI bus, etc.). After receiving a valid response on the bus, write the write buffer data read from the DMA write transfer arbitration unit 22 to the external memory;

[0065] The DMA write transfer arbitration unit 22 is used to be responsible for the arbitration of the DMA write request signal and to recei...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com