Method for analyzing fatigue life of electronic packaging welding spot

A fatigue life analysis, electronic packaging technology, used in electronic circuit testing, measuring electricity, measuring devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

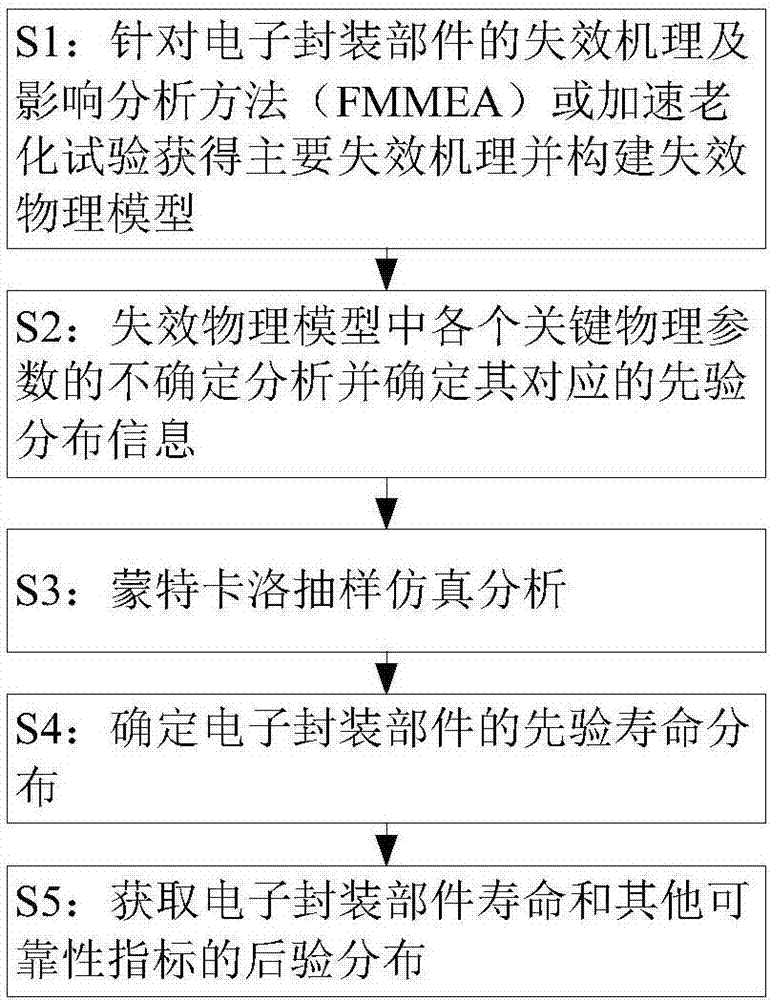

Method used

Image

Examples

Embodiment Construction

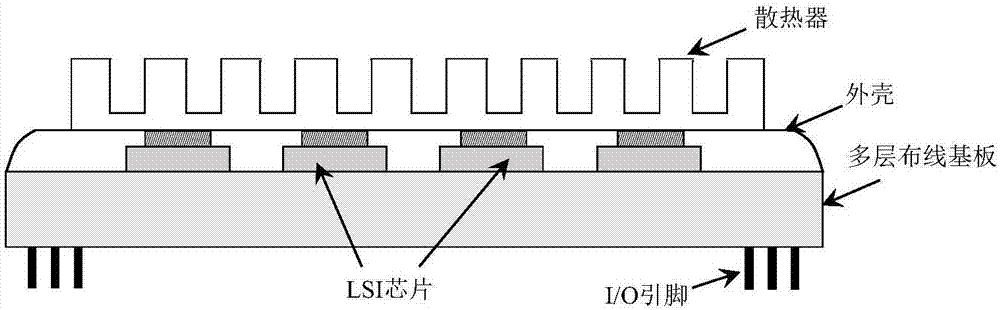

[0022] In order to facilitate those skilled in the art to understand the technical content of the present invention, the present invention will be further explained in conjunction with the accompanying drawings and specific embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

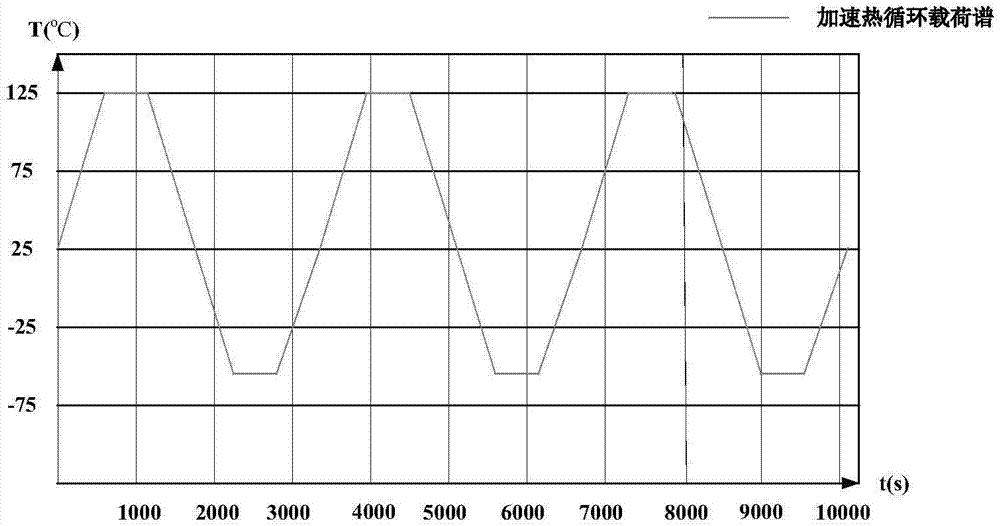

[0023] The failure physical model of components can be used to describe the relationship between the failure time of components and various influencing factors that cause component failure. Therefore, establishing a failure physical model of solder joints of multi-chip components can be used to analyze the relationship between various internal and external factors on the fatigue life of solder joints. However, each parameter in the failure physics model is not deterministic, but is affected by various uncertain factors instead. For example, the variability of the material properties itself, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com