A kind of semiconductor device and its preparation method, electronic device

A semiconductor and device technology, applied in the field of semiconductor devices and their preparation methods, and electronic devices, can solve problems such as uneven oxide height, uneven threshold voltage of semiconductor devices, device performance and yield decline, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

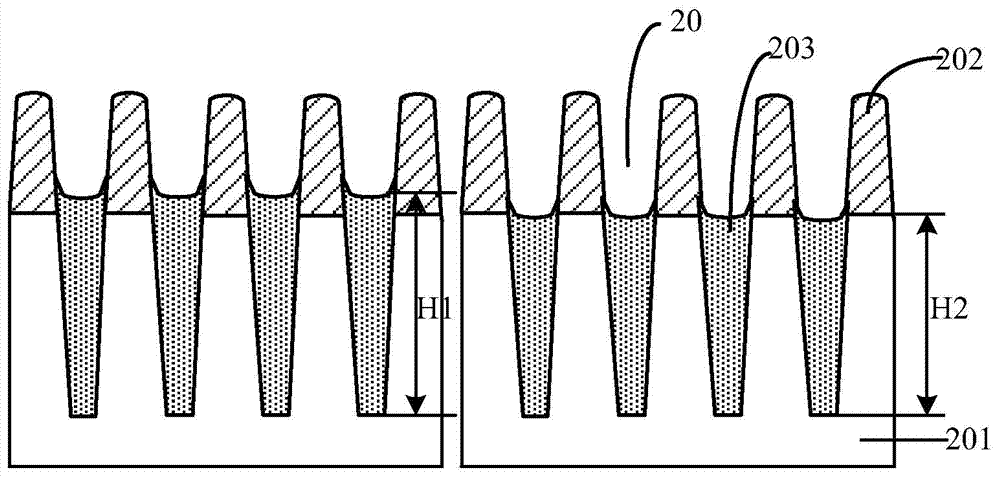

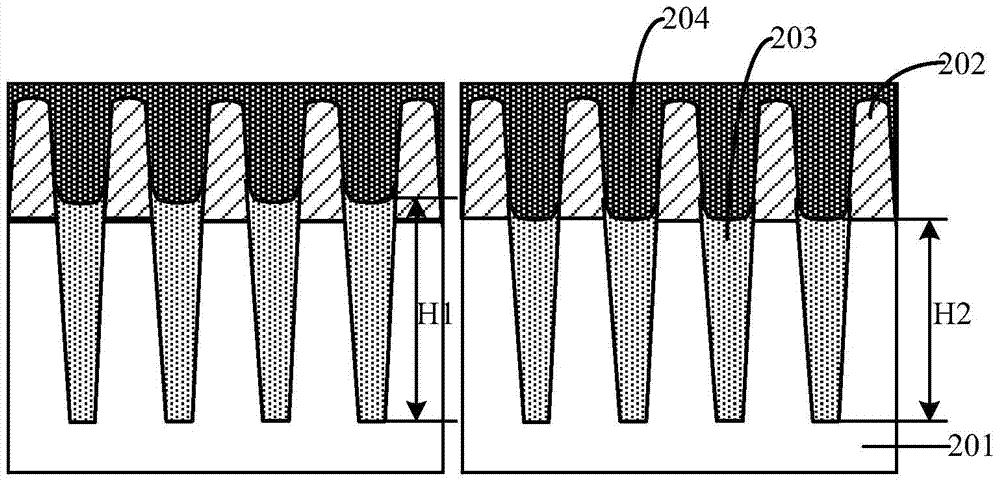

[0041] Attached below Figure 2a-2c The method for preparing the semiconductor device of the present invention is further described.

[0042] Firstly, step 201 is performed to provide a wafer in which a semiconductor substrate 201 is formed.

[0043] Specifically, such as Figure 2a As shown, wherein the wafer includes a central region and an edge region.

[0044] Wherein, the semiconductor substrate 201 may be at least one of the materials mentioned below: silicon, silicon-on-insulator (SOI), silicon-on-insulator (SSOI), silicon-germanium-on-insulator (S-SiGeOI) , silicon germanium on insulator (SiGeOI) and germanium on insulator (GeOI), etc.

[0045] Step 202 is performed to form a floating gate layer and a mask layer on the semiconductor substrate, and pattern them to form a floating gate structure 202 and a shallow trench.

[0046] Specifically, such as Figure 2a As shown, a floating gate layer is formed on the semiconductor substrate, and the floating gate layer may b...

Embodiment 2

[0077] The present invention also provides a semiconductor device, which is prepared by the method described in Embodiment 1. The isolation oxide in the edge region and central region of the semiconductor device prepared by the method of the present invention has a uniform thickness, so that the semiconductor device has a uniform threshold voltage and improves the performance and yield of the semiconductor device.

Embodiment 3

[0079] The present invention also provides an electronic device, including the semiconductor device described in Embodiment 2. Wherein, the semiconductor device is the semiconductor device described in Embodiment 2, or the semiconductor device obtained according to the preparation method described in Embodiment 1.

[0080] The electronic device of this embodiment can be any electronic product or equipment such as mobile phone, tablet computer, notebook computer, netbook, game console, TV set, VCD, DVD, navigator, camera, video recorder, voice recorder, MP3, MP4, PSP, etc. , can also be any intermediate product including the semiconductor device. The electronic device according to the embodiment of the present invention has better performance due to the use of the above-mentioned semiconductor device.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com