Synchronous demodulator, power standard source comprising synchronous demodulator and control method of power standard source

A technology of synchronous demodulator and control method, which is applied in the direction of instruments, measuring devices, and measuring electric variables, etc., which can solve the problems of slow system response, long sampling time, and large calculation amount, and achieve fast system response, short sampling time, The effect of small amount of calculation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

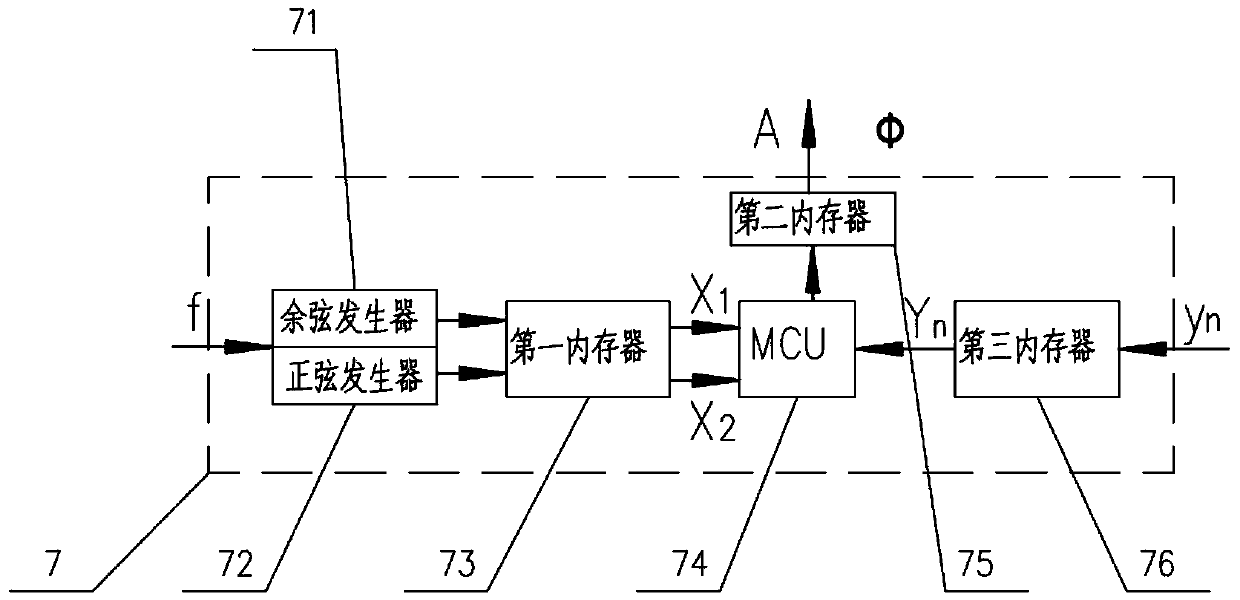

[0067] A synchronous demodulator, see figure 1 , specifically including a cosine generator 71 , a sine generator 72 , a first memory 73 , an MCU 74 , a second memory 75 and a third memory 76 .

[0068] The cosine generator 71 and the sine generator 72 are arranged in parallel, and the output ends of both are connected to the input end of the first memory 73 .

[0069] The output end of the first memory 73 is connected with the first input end of the MCU 74 .

[0070] The second input end of the MCU 74 is connected to the output end of the third memory 76 .

[0071] The output terminal of the MCU 74 is connected with the input terminal of the second memory 75 .

[0072] The MCU74 is provided with a digital signal processor DSP.

[0073] The control method of the above-mentioned synchronous demodulator includes the following steps:

[0074] The first step: the cosine generator 71 and the sine generator 72 generate two signal matrices X according to the set operating frequenc...

Embodiment 2

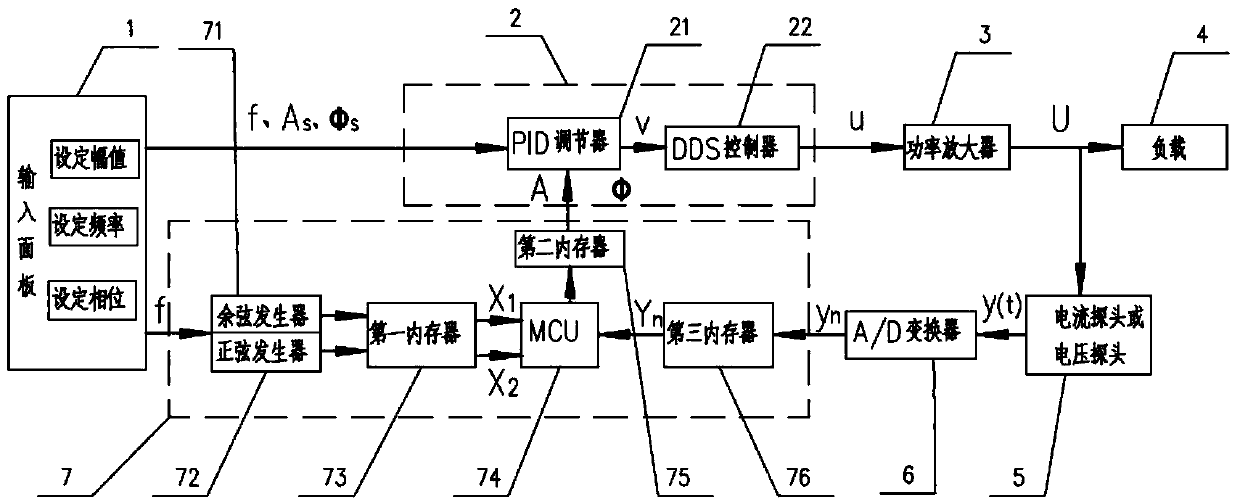

[0093] A power standard source, see figure 2 .

[0094]It specifically includes input panel 1 for setting amplitude, frequency and phase, controller 2, power amplifier 3, load 4, current probe or voltage probe 5, A / D converter 6 and synchronous demodulator 7, the overall structure streamline.

[0095] The controller 2 includes a PID regulator 21 and a DDS controller 22, and the synchronous demodulator 7 includes a cosine generator 71, a sine generator 72, a first memory 73, an MCU 74, a second memory 75 and a third A memory 76 , the cosine generator 71 and the sine generator 72 are arranged in parallel, and the output ends of both are connected to the input end of the first memory 73 .

[0096] The output end of the first memory 73 is connected to the first input of the MCU74, the second input of the MCU74 is connected to the output of the third memory 76, and the output of the MCU74 is connected to the output of the MCU74. The input end of the second memory 75 is connecte...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com