Circuit and method for generating clock pulse data reply signal phase locked index

A technology of clock pulse and signal phase, applied in the direction of electrical components, automatic power control, etc., can solve the problem of not being equal

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

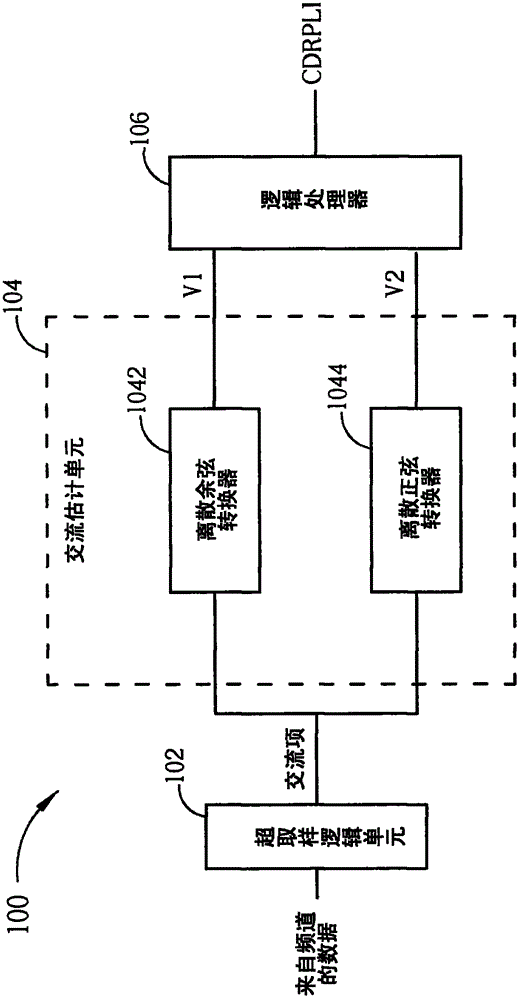

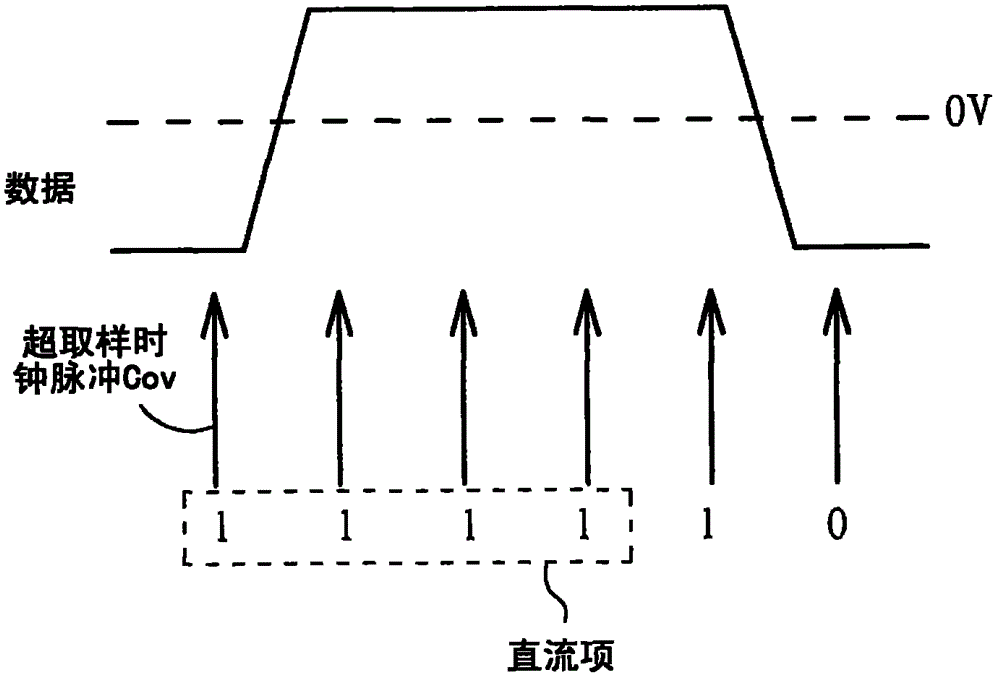

[0018] Please refer to figure 1 , figure 1 A schematic diagram of a circuit 100 for generating a phase lock indicator of a clock pulse data recovery signal is illustrated for an embodiment of the present invention. The circuit 100 includes an oversampling logic unit 102 , an AC estimation unit 104 and a logic processor 106 . The over-sampling logic unit 102 is used to perform an over-sampling operation on data from a channel according to an over-sampling clock Cov to generate a plurality of AC terms, and according to an output clock Co, A plurality of AC terms associated with the output clock Co is output from the plurality of AC terms. In addition, the frequency of the oversampling clock Cov must be greater than twice the frequency of the data. In this embodiment, the oversampling clock Cov is 10 GHz and the data frequency is 2.5 GHz, but the present invention is not limited to the oversampling clock Cov being 10 GHz and the data frequency being 2.5 GHz.

[0019] Please r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com