Partial silicon on insulator (PSOI) lateral super-junction power semiconductor device

A lateral super-junction power and semiconductor technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of reducing the withstand voltage of SOI lateral super-junction devices, charge imbalance, etc., to eliminate the substrate-assisted depletion effect, improve Charge balance, improve the effect of withstand voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

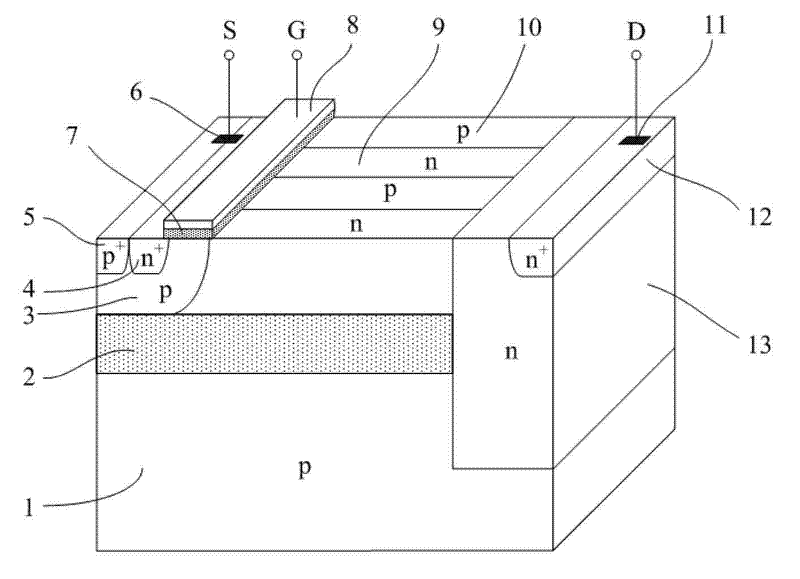

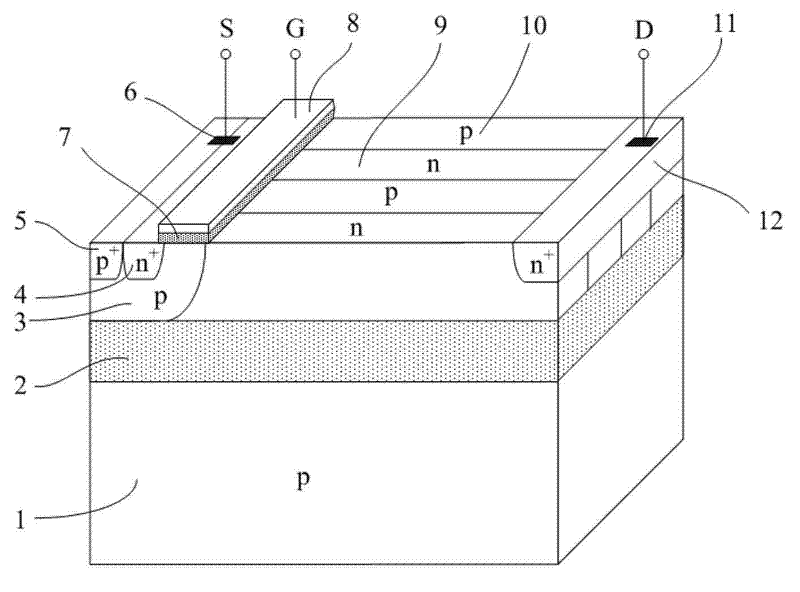

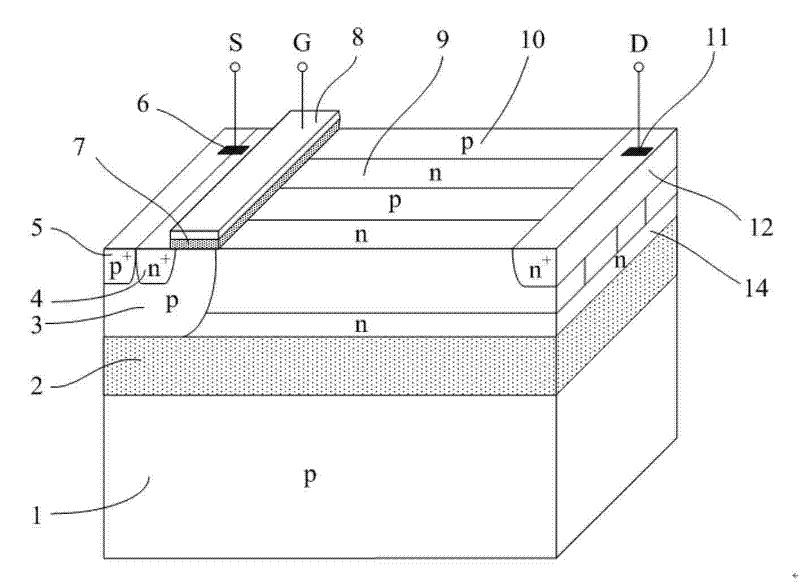

[0015] Attached below figure 1 The present invention will be described in detail.

[0016] A PSOI lateral superjunction power semiconductor device according to the present invention comprises a p-type substrate 1, an insulating buried layer 2 is arranged on the upper end surface of the p-type substrate 1, and a p-type body region 3 is arranged on the upper end surface of the insulating buried layer 2 And the super junction structure, the super junction structure is composed of super junction n regions 9 and super junction p regions 10 distributed alternately in the lateral direction, the p type body region 3 is in contact with one side of the super junction structure, and the p type body region 3 is provided with n Type source region 4, p-type body contact region 5 and gate oxide layer 7, polysilicon gate 8 is arranged on the upper end of gate oxide layer 7, source electrode 6 is arranged on n-type source region 4 and p-type body contact region 5, super junction The other si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com