Testing method of digital protection tester with fault data model base for protection testing

A technology of fault data and testing methods, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as protection malfunctions, problems that have occurred or are very likely to occur, and that the time is not long

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The function definitions of the front panel and rear panel of the digital protection tester are shown in the table below:

[0036] Terminal function definition table on the front and rear panels of the device

[0037]

[0038]

[0039] Hardware composition:

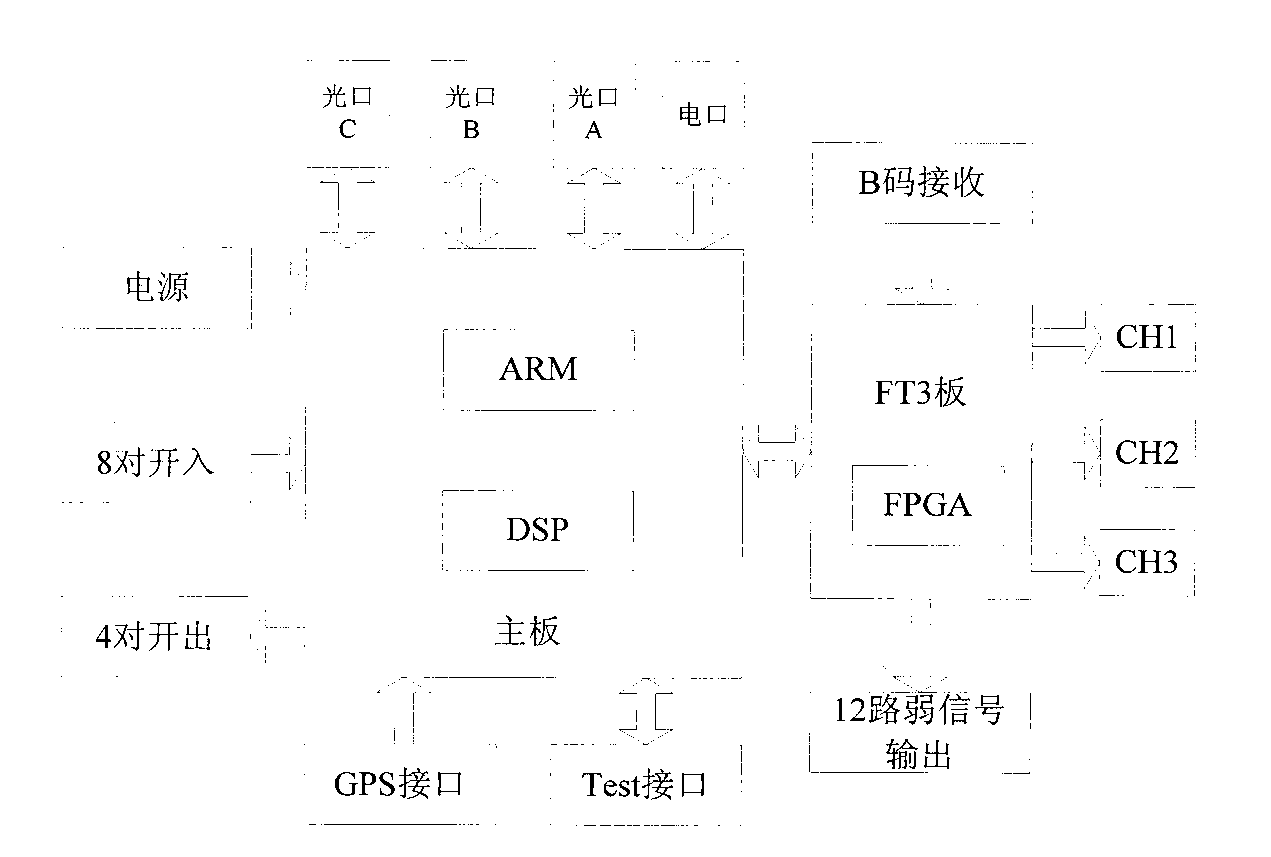

[0040] The tester uses 32-bit embedded ARM (Advanced RISC Machines) and digital signal processor (DSP) to realize Ethernet communication function and efficient and fast data processing function, field programmable gate array FPGA (Field Programmable Gate Array) controls FT3 report Text output and optical B code reception, hardware composition see figure 1 .

[0041] The tester ARM uses 10 / 100M Ethernet port to connect with the upper computer, and uses optical fiber Ethernet to output data packets to the digital protection device under test. There are 8 switch input ports and 4 switch output ports designed on the tester panel. When the protected outlet circuit under test adopts hard wiring, eight pairs of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com