Clock generating and smoothing device

A smoothing device and clock technology, applied in the field of communication, can solve the problems of misjudgment, bit error, PDH signal clock irregularity of downstream chips, etc., and achieve the effect of avoiding bit error and smoothing the clock signal

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

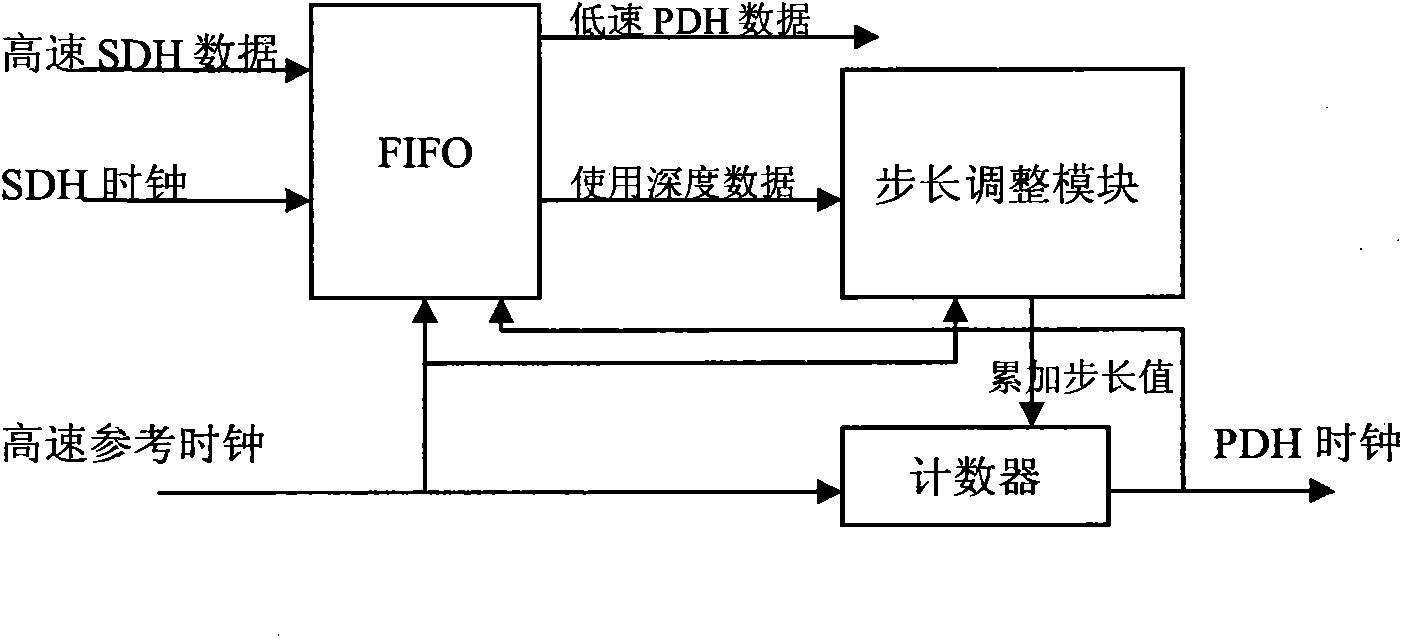

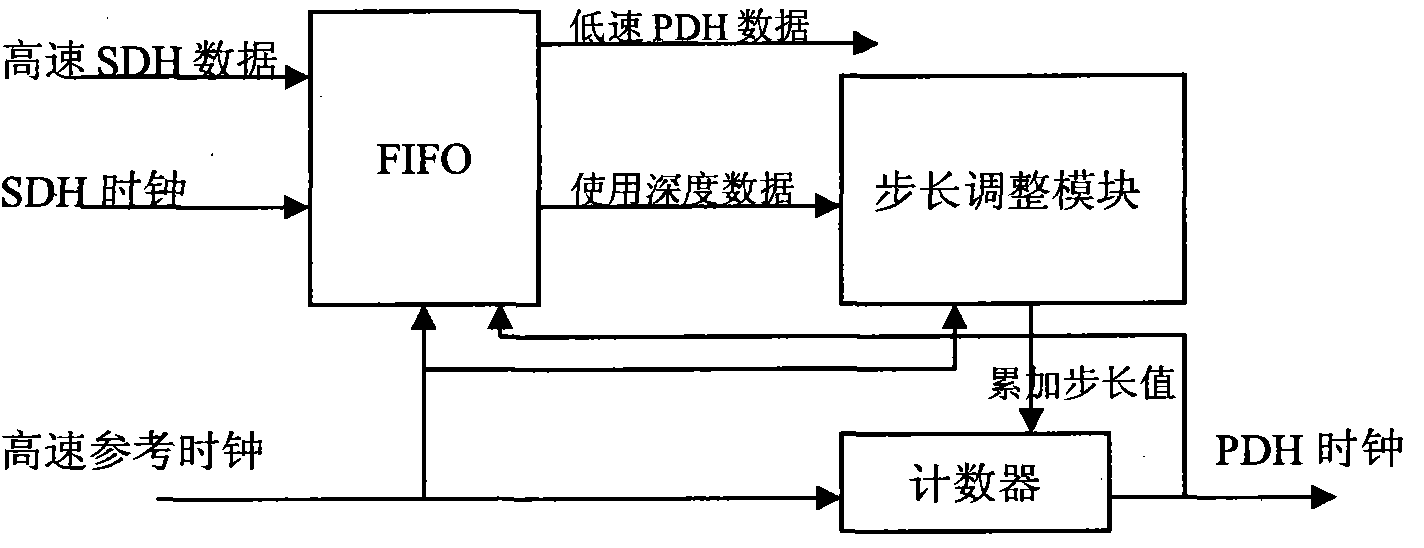

[0008] The realization principle of the clock smoothing function of a clock generation and smoothing device of the present invention is: when the FIFO depth exceeds a certain value, it means that the read clock rate of the FIFO is too low, and the step size adjustment module increases the step size, thereby outputting the clock rate increase; when the depth of the FIFO used is less than a specified value, the step size adjustment module reduces the step size, thereby slowing down the output clock rate, thereby smoothing the overall rate of the generated clock signal.

[0009] See attached figure 1 , a kind of clock generation and smoothing device of the present invention, comprise FIFO, step size adjustment module and register, high-speed SDH data is as the input data of described FIFO, SDH clock is as the write clock of FIFO, and high-speed reference clock is as read clock, uses For reading the data in the FIFO, the step adjustment module and the counter, the data read from t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com