Insulated gate semiconductor device and method for manufacturing the same

一种绝缘栅型、制造方法的技术,应用在半导体/固态器件制造、半导体器件、晶体管等方向,能够解决导通特性恶化、不能够抑制二极管正向电压上升等问题,达到提高导通特性、抑制正向电压Vf、抑制恢复电流的上升的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

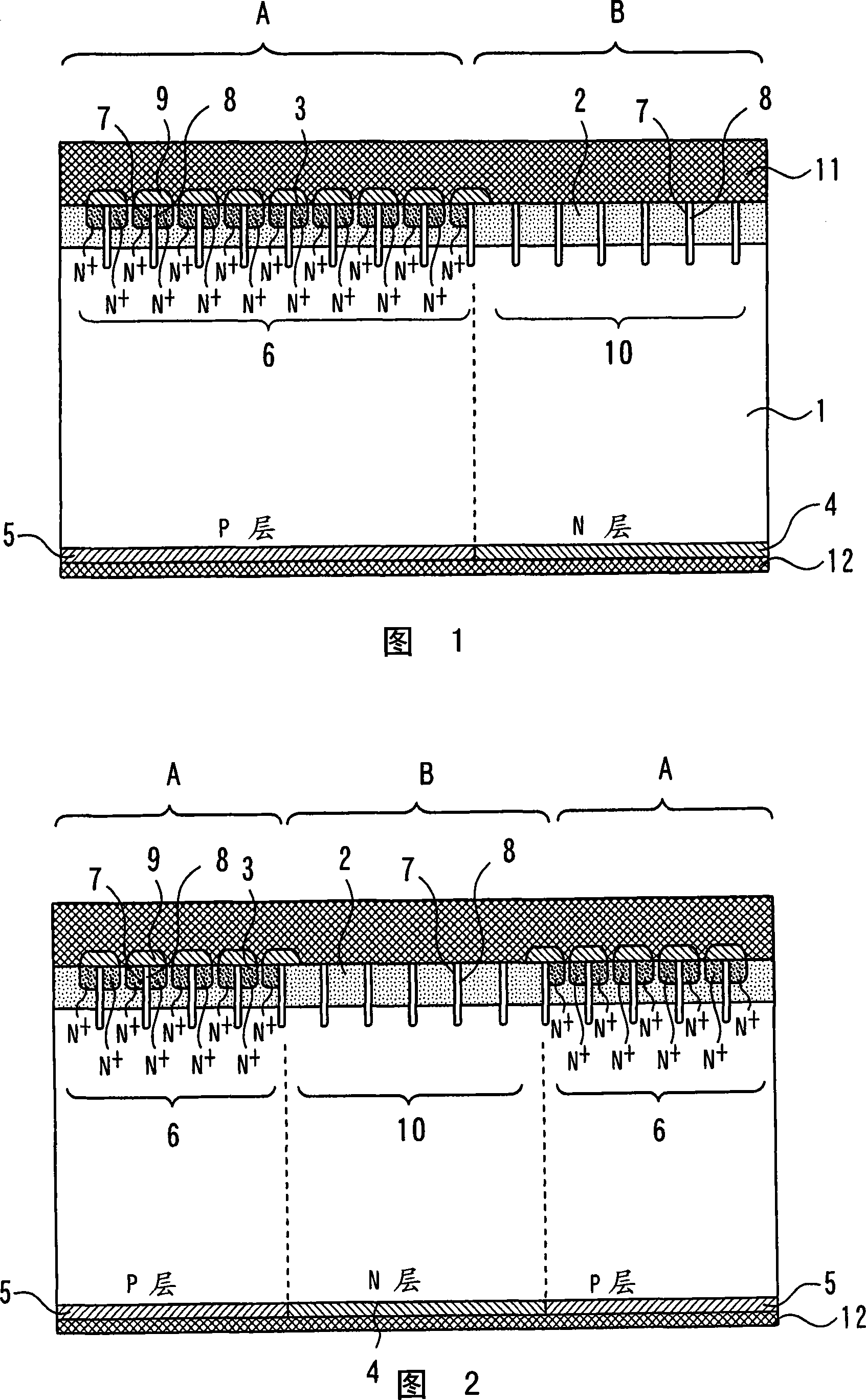

[0070] FIG. 1 shows a cross-sectional view of an insulated gate semiconductor device according to Embodiment 1. As shown in FIG. Using N with N-type impurities - substrate 1 forming the semiconductor device, N - The substrate 1 has a first main surface (upper main surface) and a second main surface (lower main surface). N - The substrate 1 has at least one region A (first region), and a region B (second region) is provided adjacent thereto. The emitter layer 3 is provided on the region A, while the emitter layer 3 is not provided on the region B.

[0071] In area A and area B, in N - In the vicinity of the first main surface side of the substrate 1, a P base layer 2 in which P-type impurities are diffused is selectively provided. On area A, from N - The first main surface of the substrate 1 penetrates the P base layer 2, and a plurality of first grooves 6 are provided at intervals of about 2 to 10 μm (and, as shown in FIG. - When a plurality of regions A are provided on...

Embodiment approach 2

[0097] An insulated gate semiconductor device according to Embodiment 2 will be described with reference to FIG. 9 . Here, description will focus on differences from Embodiment 1. FIG.

[0098] As shown in Figure 9, at N - On the second main surface side of the P base layer 2 of the substrate 1 , a carrier accumulating layer 13 is provided as a fifth semiconductor layer containing N-type impurities so as to be in contact with the P base layer 2 . The N-type impurity concentration ratio of the carrier accumulation layer 13 is N - The impurity concentration of the substrate 1 is high. Other configurations are the same as those in Embodiment 1.

[0099] Next, the operation of the insulated gate semiconductor device shown in FIG. 9 will be described. The operation of the IGBT shown in FIG. 9 is basically the same as that of the IGBT shown in FIG. 1 . When the IGBT shown in FIG. 9 is in operation, the carrier accumulation layer 13 serves as a barrier layer for holes injected f...

Embodiment approach 3

[0105] An insulated gate semiconductor device according to Embodiment 3 will be described with reference to FIG. 10 . Here, description will focus on differences from Embodiments 1 and 2. FIG.

[0106] In the insulated gate type semiconductor device shown in FIG. 10 , the impurity concentration of P base layer 2 provided on region A is different from the impurity concentration of P base layer 2 b provided on region B. Specifically, the impurity concentration of the P base layer 2b in the region B is lower than the impurity concentration of the P base layer 2 provided in the region A. Other structures are the same as those in Embodiment 1.

[0107] The operation of the IGBT in FIG. 10 is basically the same as that of the IGBT in FIG. 1 . In Embodiment 3, the impurity concentration of the first semiconductor layer functioning as the P base layer of the IGBT is different from that of the first semiconductor layer functioning as the anode P layer of the diode. Accordingly, the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com