Border scanning test structure of multiple chip package internal connection and test method

A technology of boundary scan testing and multi-chip packaging, which is applied in the fields of integrated circuit chip design and chip testability design, can solve problems such as connection between chips, and achieve the effect of reducing chip program writing time and shortening test time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

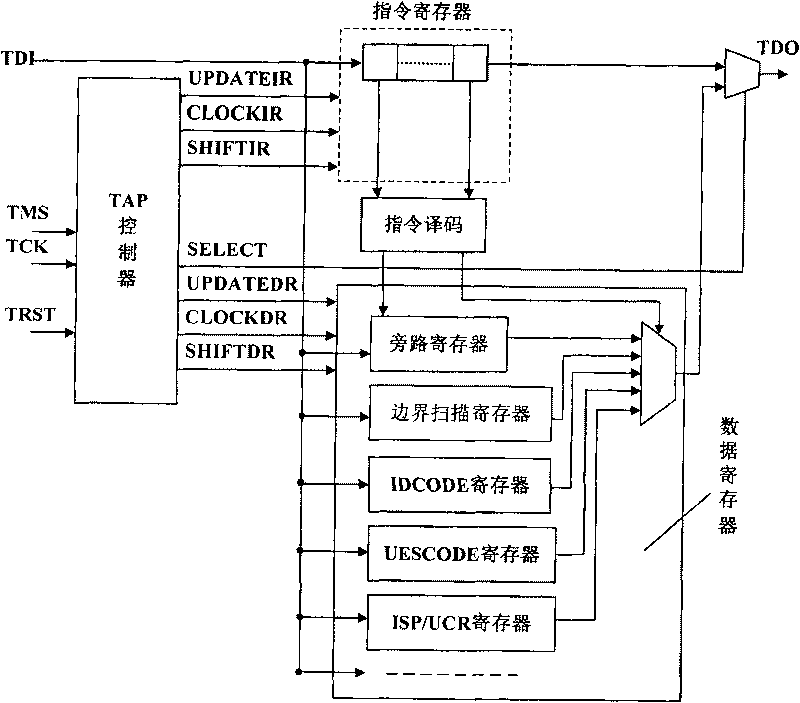

[0036] figure 1 It is a typical boundary scan test circuit structure diagram. However, under the requirements of the special products targeted by the present invention, that is, the number of chips in the package is large, the connection relationship is complicated, and the number of pins connected to the outside of the package is extremely limited. For example, in smart card products, there are only 8 external connection pins. The traditional 4 (or 5) boundary scan dedicated test pins TDI, TDO, TCK, TMS and TRST (optional pins) on the chip in the package cannot be directly connected to the outside of the package.

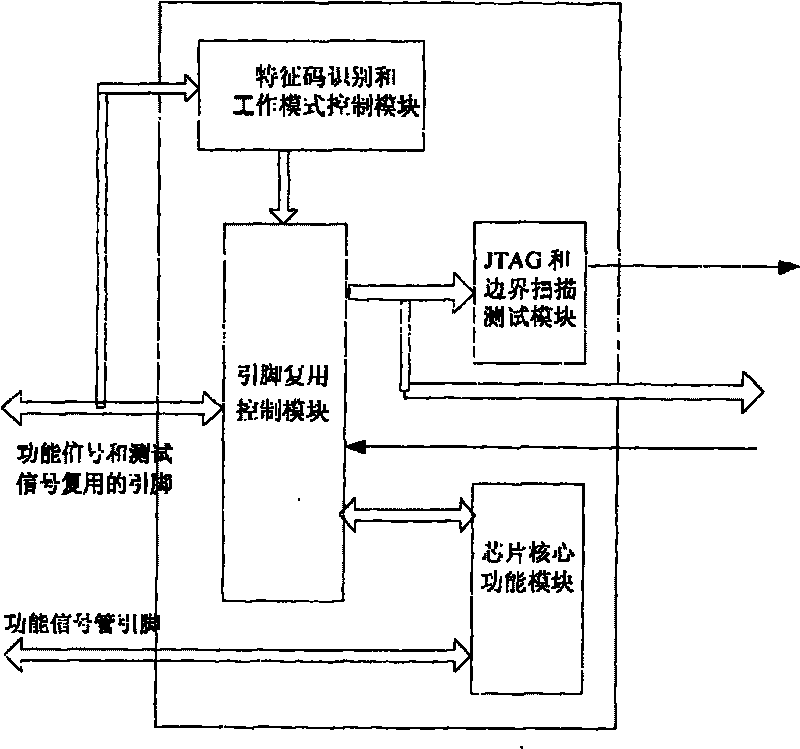

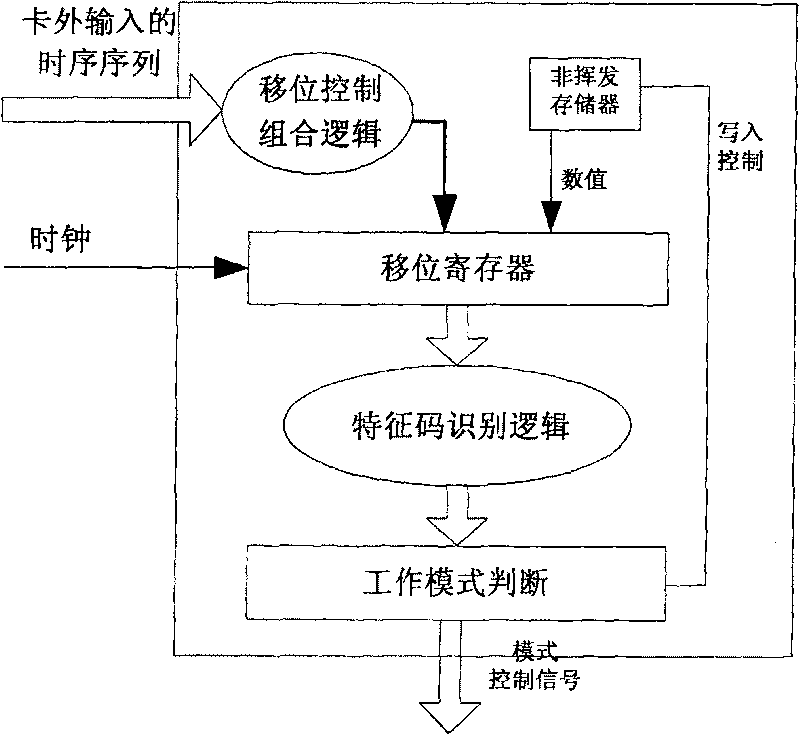

[0037] figure 2 A solution under the special complex conditions mentioned above is given. The five pins required for JTAG and boundary scan will be multiplexed with the normal operating signal pins of the package when the circui...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com