Rebuilt-up device for digital asynchronous clock

An asynchronous clock and digital technology, applied in baseband system components, transmitter/receiver shaping network, etc., can solve the problems of reducing the accuracy of digital-to-analog conversion, digital information loss, misalignment, etc., to improve the clock jitter problem , low jitter characteristics, and the effect of extending the distance

Inactive Publication Date: 2009-11-18

BEIHANG UNIV

View PDF5 Cites 0 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

[0002] During the processing and transmission of digital signals, additional clock jitter is often added. Although these clock jitters will not affect the correctness of data content, they can reduce the accuracy of digital-to-analog conversion.

If the clock jitter is too serious, it may also cause the loss or dislocation of digital information in the communication process

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment

[0035] Example: Used to eliminate clock jitter during serial communication

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

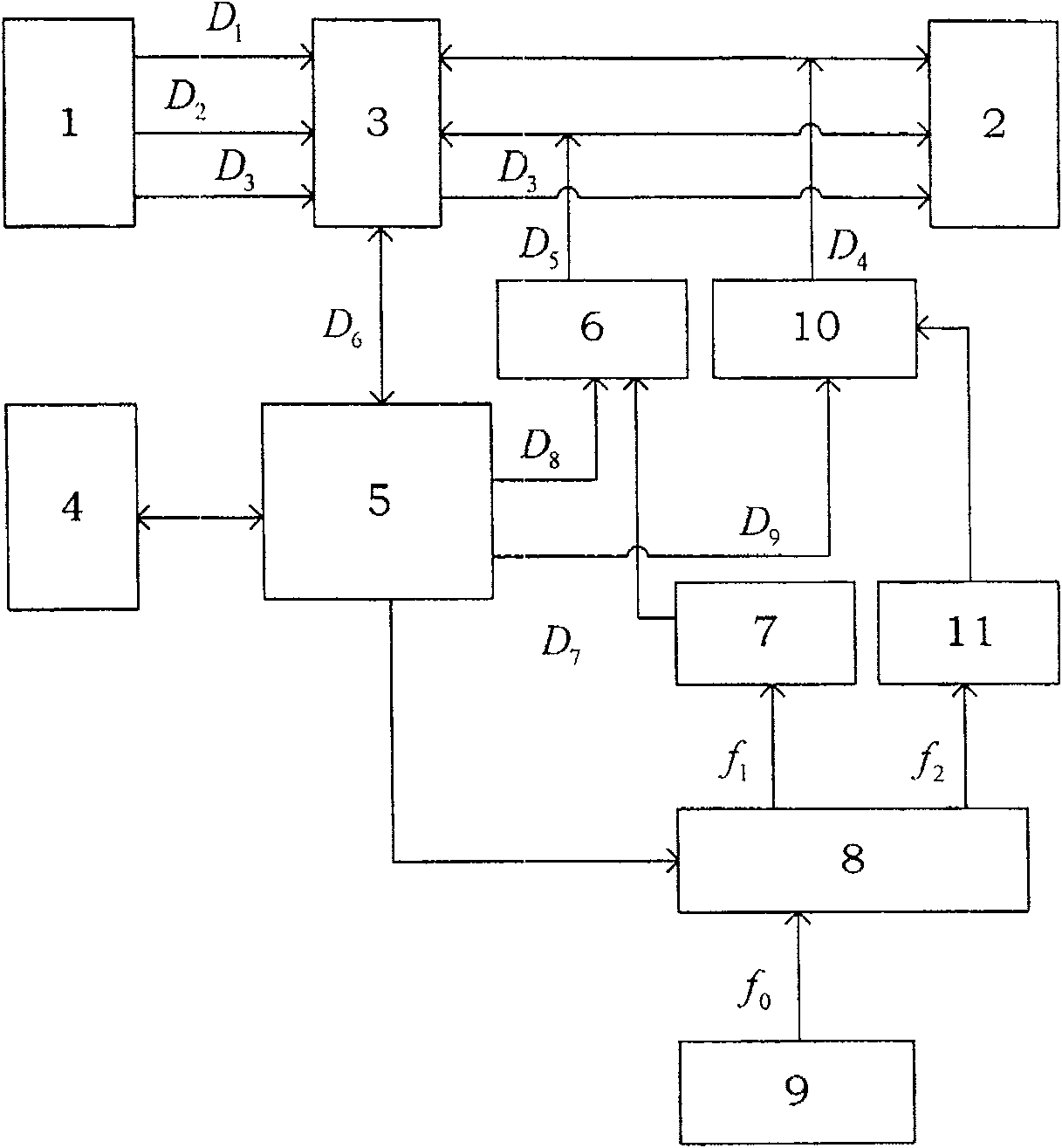

The invention discloses a digital asynchronous clock rebuilding device, which comprises a digital signal input interface, a digital signal output interface, an asynchronous FIFO memory, a non-volatile memory, a general processor, a first clock distributor, a second clock distributor, a It is composed of a band-pass filter, a second band-pass filter, a digital frequency synthesizer and a high-speed crystal oscillator; the device of the present invention makes the clock of the input digital signal and the clock of the output digital signal independent of each other, aiming at the difference of the clock jitter of the input digital signal Determine the problem, use the asynchronous buffer mechanism to delay the output data relative to the input data, so that when there is a short-term frequency or phase difference between the input digital signal clock and the output digital signal clock, use DDS to regenerate the output clock, and use the clock distribution chip to further Improve the quality of the output clock. The output frequency of the DDS is fine-tuned by a general-purpose processor, thereby eliminating the long-term frequency difference between the input digital signal clock and the output digital signal clock, and avoiding the asynchronous buffer from overflowing or being completely empty. This ensures that the jitter of the output digital signal clock has nothing to do with the jitter of the input clock, and is only affected by the output jitter performance of the multi-channel DDS chip and the clock distribution chip.

Description

technical field [0001] The present invention relates to an asynchronous clock reconstruction device, more particularly, to an asynchronous clock reconstruction device for eliminating digital signal clock jitter. Background technique [0002] During the processing and transmission of digital signals, additional clock jitter is often added. Although these clock jitters will not affect the correctness of data content, they can reduce the accuracy of digital-to-analog conversion. If the clock jitter is too serious, it may also cause the loss or dislocation of digital information in the communication process. Contents of the invention [0003] The object of the present invention is to provide a digital asynchronous clock rebuilding device, the device makes the clock of the input digital signal and the clock of the output digital signal independent of each other, and rebuilds a low-jitter asynchronous clock according to the digital signal and clock input externally, thereby real...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Patents(China)

IPC IPC(8): H04L25/02H04L25/03

Inventor 陈培

Owner BEIHANG UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com