Quickly configuration method of field programmable gate array

A gate array and configuration data technology, applied in the computer field, can solve the problem of high price, achieve the effect of less operation, fast configuration speed and cost reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

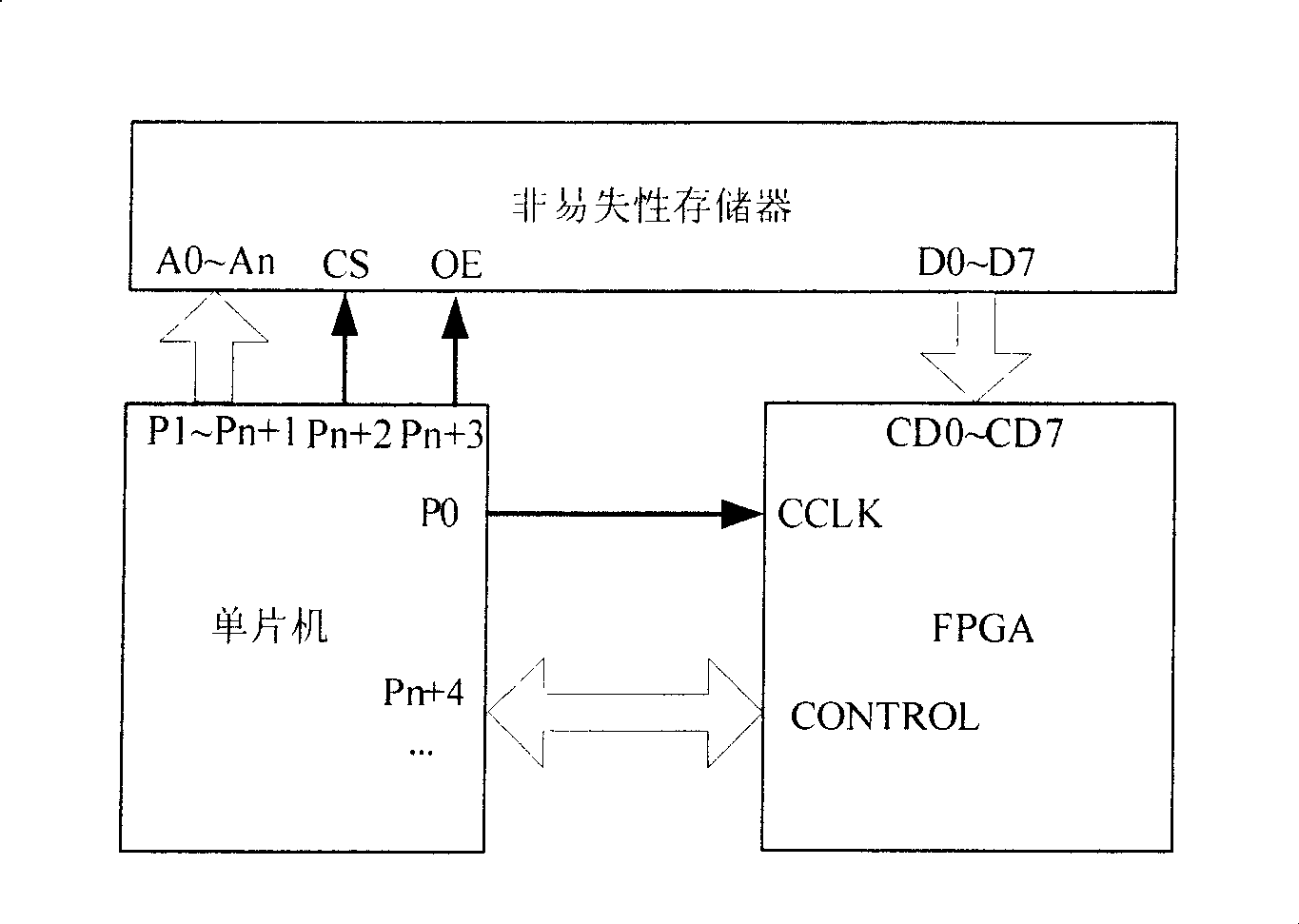

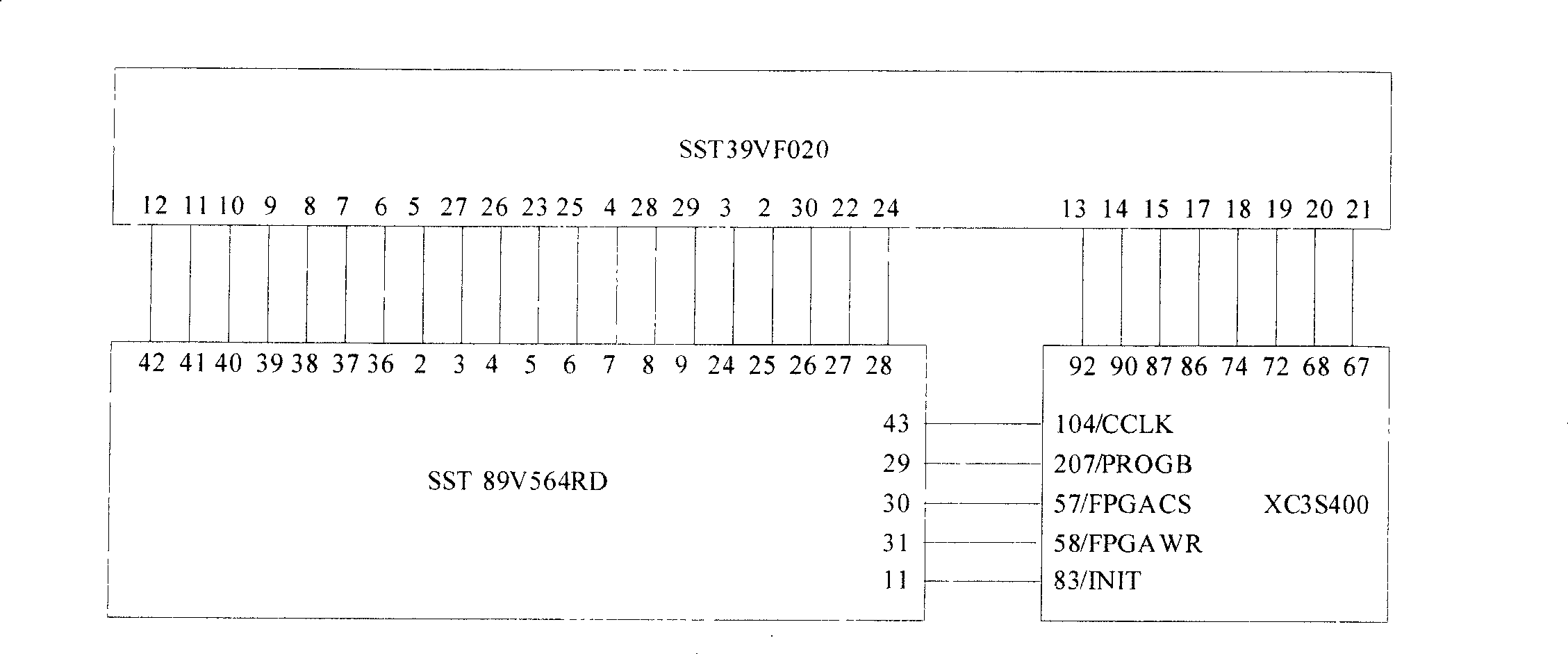

[0022] refer to figure 1 As shown, the single-chip microcomputer in the figure refers to a single-chip microcomputer with an internal program memory. If a single-chip microcomputer without an internal program memory is used, an external program memory should be added to store the single-chip program. Single-chip microcomputer means that the number of I / O pins of the single-chip microcomputer is not less than the sum of the number of non-volatile memory addresses, chip select and output enable pins, and the number of configuration control pins of the FPGA to be configured. If the single-chip I / O pins If the number is less than the sum of the number of non-volatile memory addresses, chip select and output enable pins, and the number of configuration control pins of the FPGA to be configured, the number of I / O pins must be expanded by means of latches, etc., so that the expanded After the total number of I / O pins meet the requirements.

[0023] A0~An in the non-volatile memory m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com