5+3 levels pipeline structure and method in RISC CPU

A design method and assembly line technology, applied in the direction of program control design, calculation, instruments, etc., can solve the problems of reducing efficiency, increasing costs, increasing hardware, etc., to achieve the goal of saving chip area, improving processing speed and work efficiency, and great flexibility Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] DETAILED DESCRIPTION OF THE INVENTION The present invention will be described in detail below with reference to a specific embodiment of the present invention.

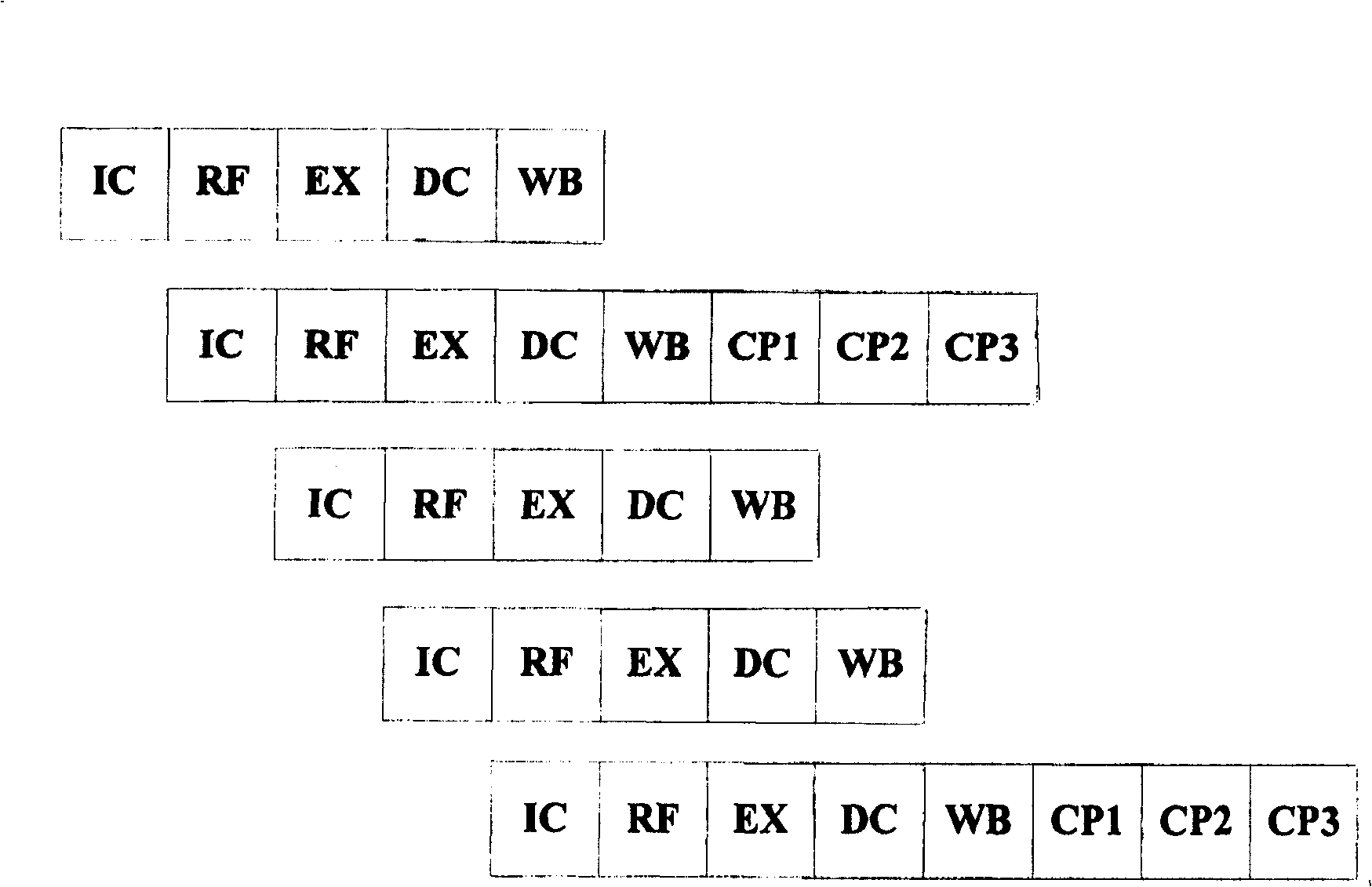

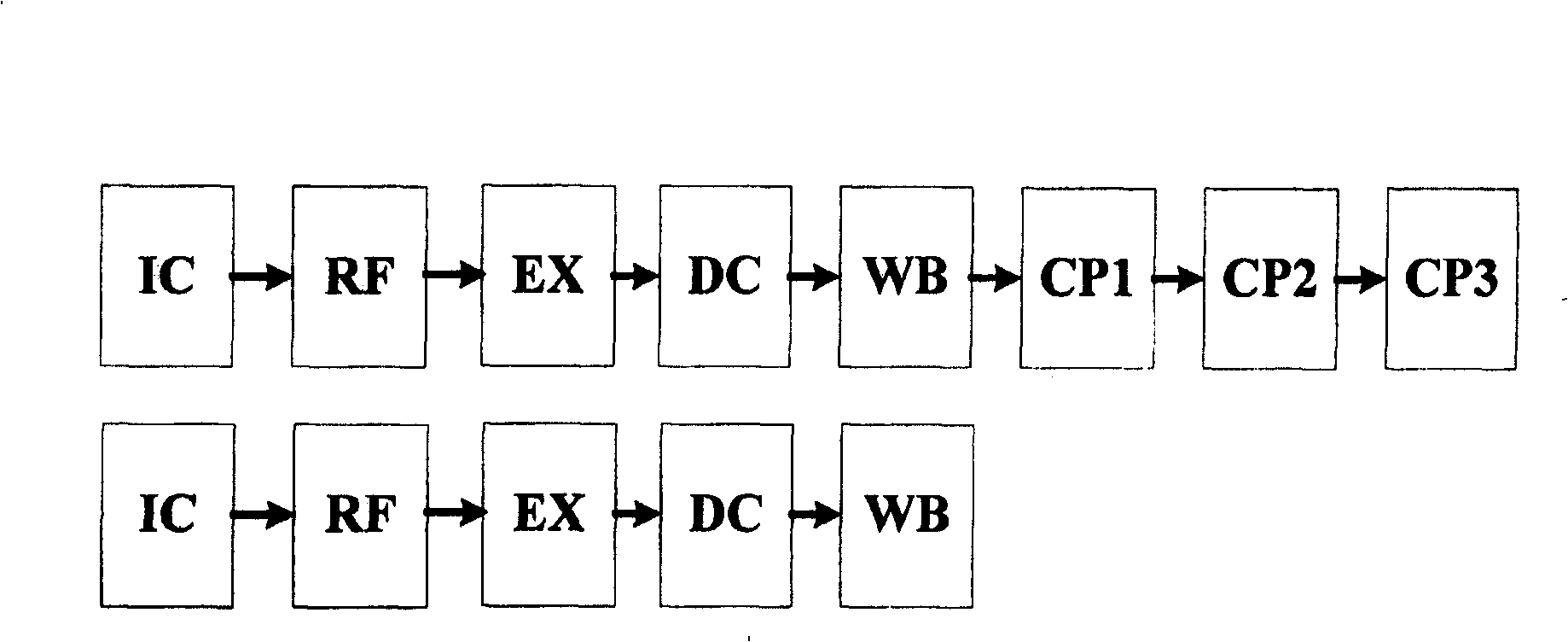

[0032] attached figure 1 Shown is a schematic diagram of the execution sequence of a five-stage pipeline for commonly used instructions. As shown in the figure, the instructions of the CPU are divided into five stages to complete, and each stage performs a corresponding operation. Each stage of the pipeline is a clock cycle, that is, two phases .

[0033] Due to the pipeline structure, each stage of the pipeline is a clock cycle. In each clock cycle, five instructions are executed at the same time, but each instruction executes a different part. It is set at a certain clock cycle. When the first When n instructions execute the fifth step, the n+1th instruction executes the fourth step, the n+2th instruction executes the third step, and the n+3th instruction executes the second step Operation, the n+4th instru...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com