System and method for hiding memory latency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The following is intended to provide a detailed description of an example of the invention and should not be taken to be limiting of the invention itself. Rather, any number of variations may fall within the scope of the invention which is defined in the claims following the description.

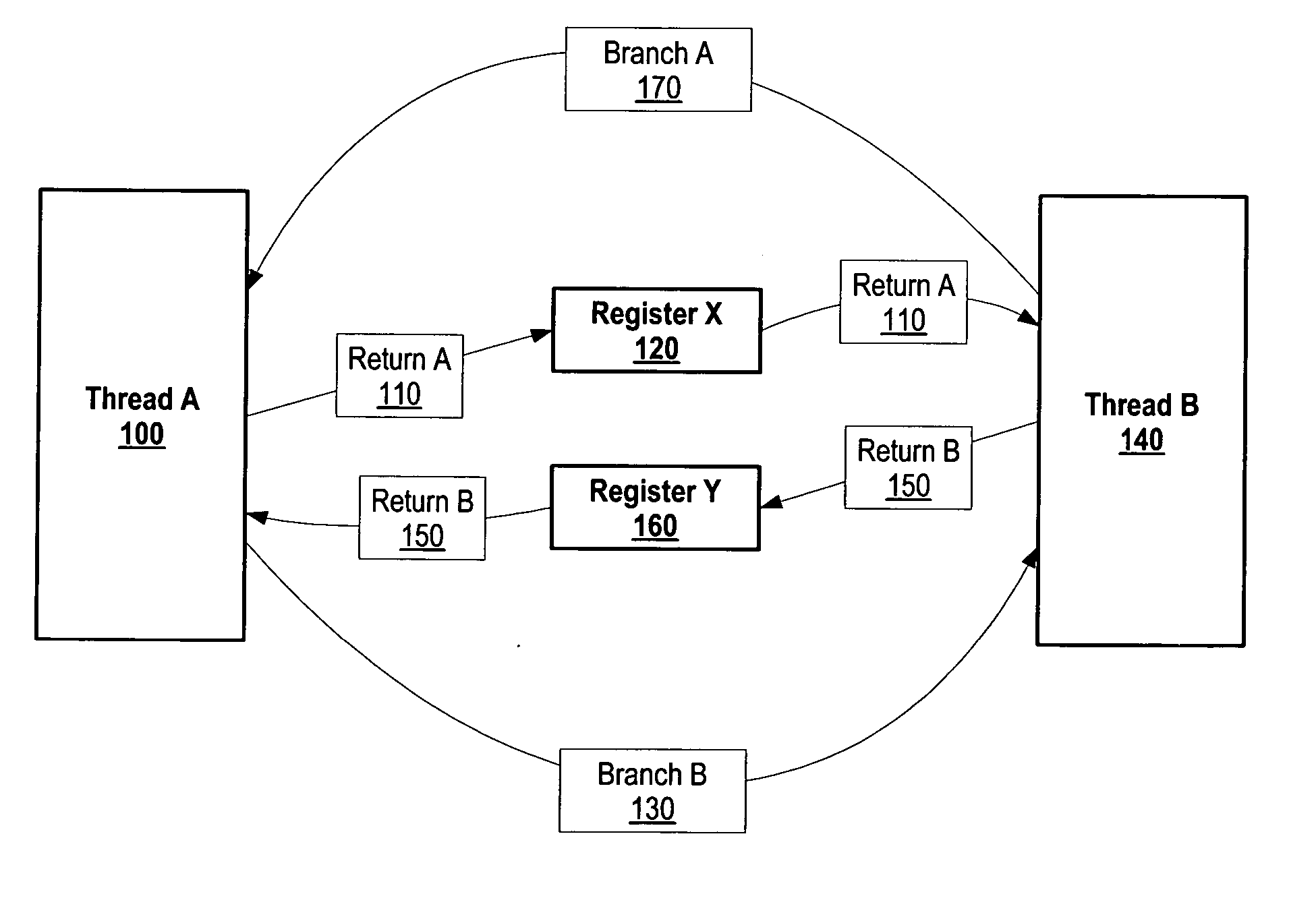

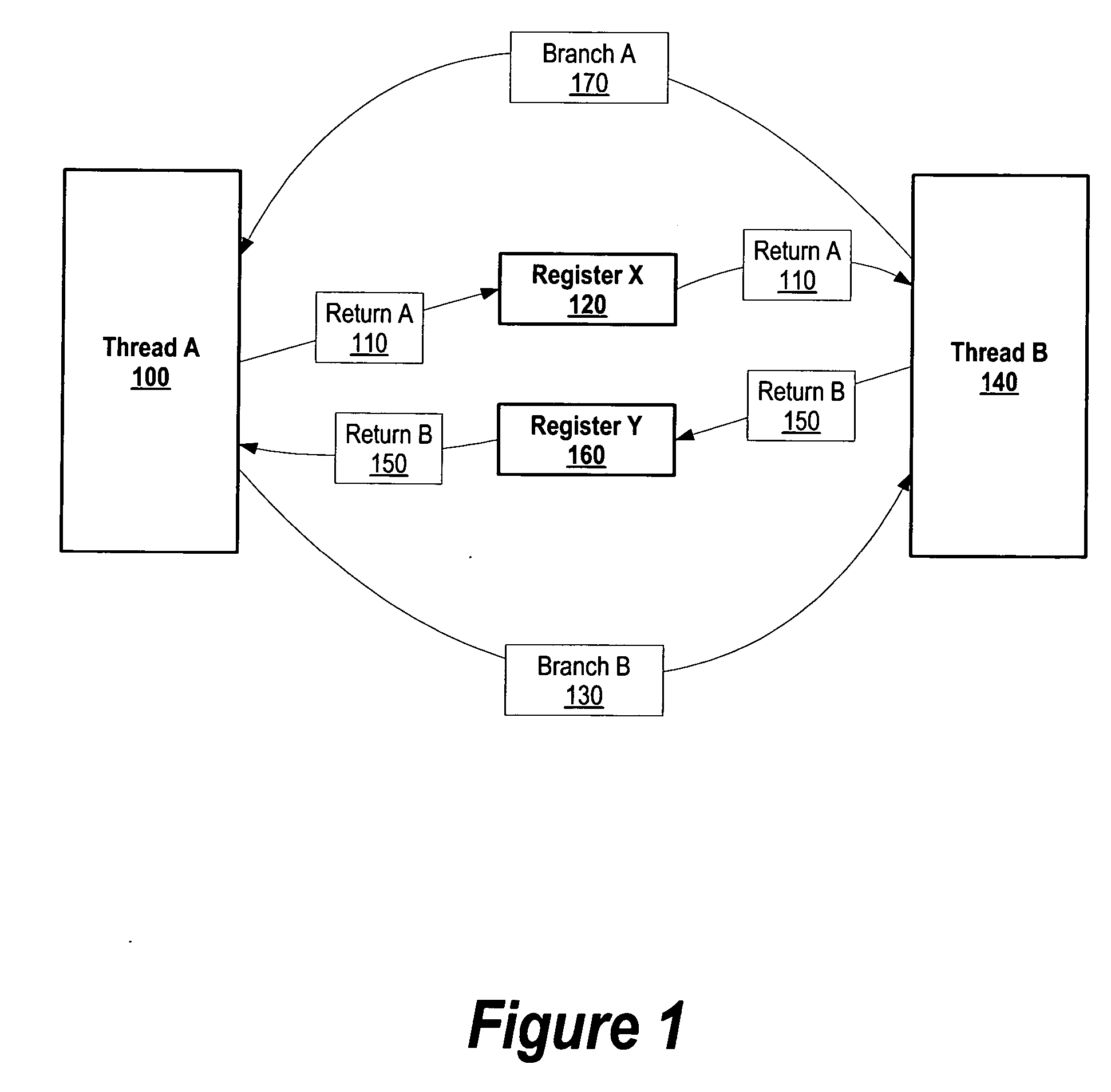

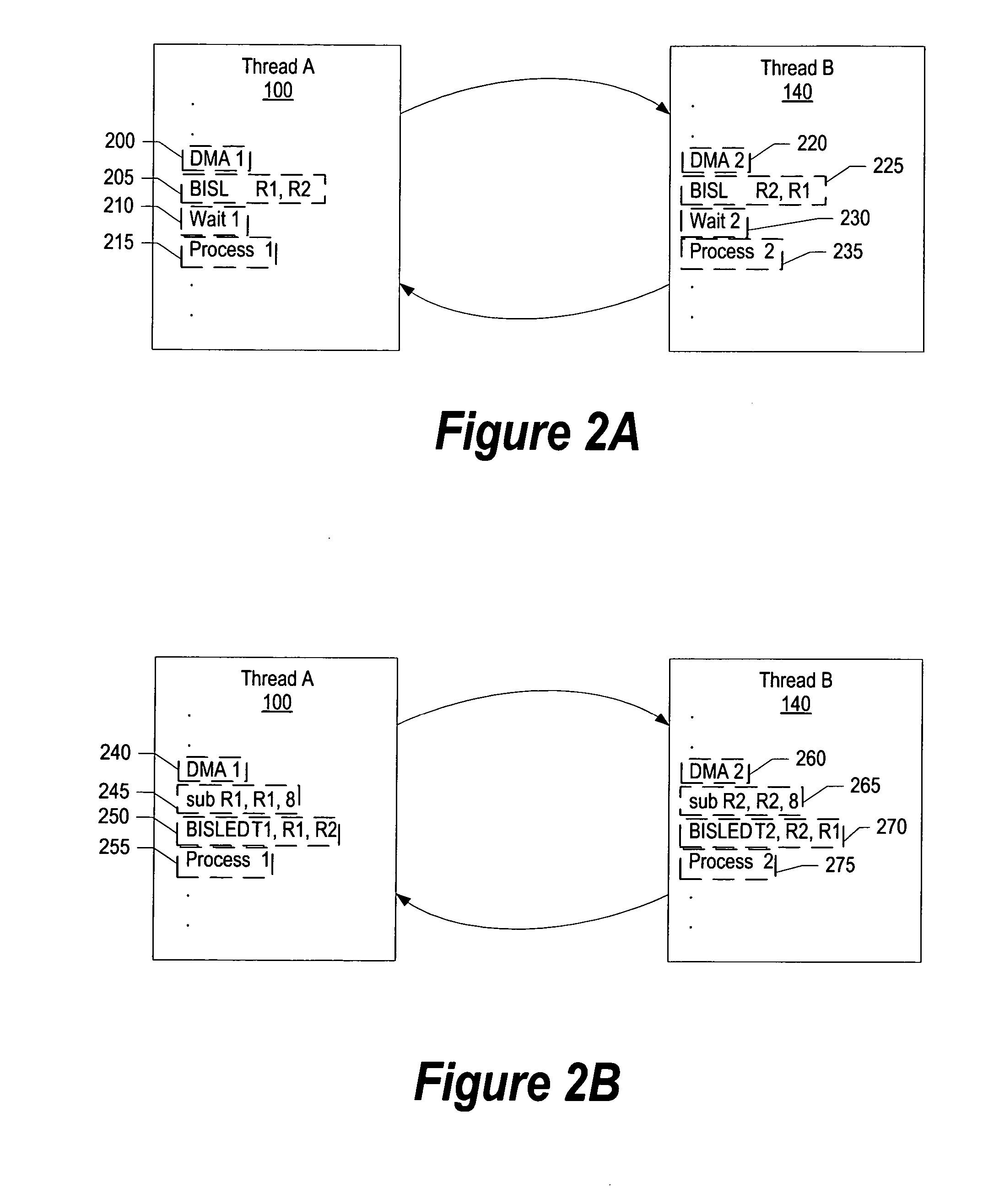

[0025]FIG. 1 is a diagram showing two threads branching to each other when the threads encounter a prolonged instruction. While the example shown in FIG. 1 includes two threads, the invention described herein is not limited to two threads and, as one skilled in the art can appreciate, the invention is applicable to any number of multiple threads. At compile time, Branch Indirect and Set Link (BISL) and / or Branch Indirect and Set Link if External Data (BISLED) instructions are placed in thread code at instances that correspond to a thread's prolonged instruction. A prolonged instruction is an instruction that may instigate latency in a computer system, such as a DMA instruction. When a first t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com