Static protection system using the floating and/or deflected multi-crystal silicon area and its method

一种静电放电保护、多晶硅的技术,应用在电路、晶体管、电气元件等方向,能够解决减小击穿电压困难、有效性受限、增加制造复杂度等问题,达到延迟时间、容易使用、减小损坏的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention relates to integrated circuits. More specifically, the present invention provides a system and method for electrostatic discharge (ESD) protection using floating and / or biased polysilicon regions. As an example, the invention has been applied to input / output (I / O) devices. However, it should be recognized that the invention has a much broader range of applicability.

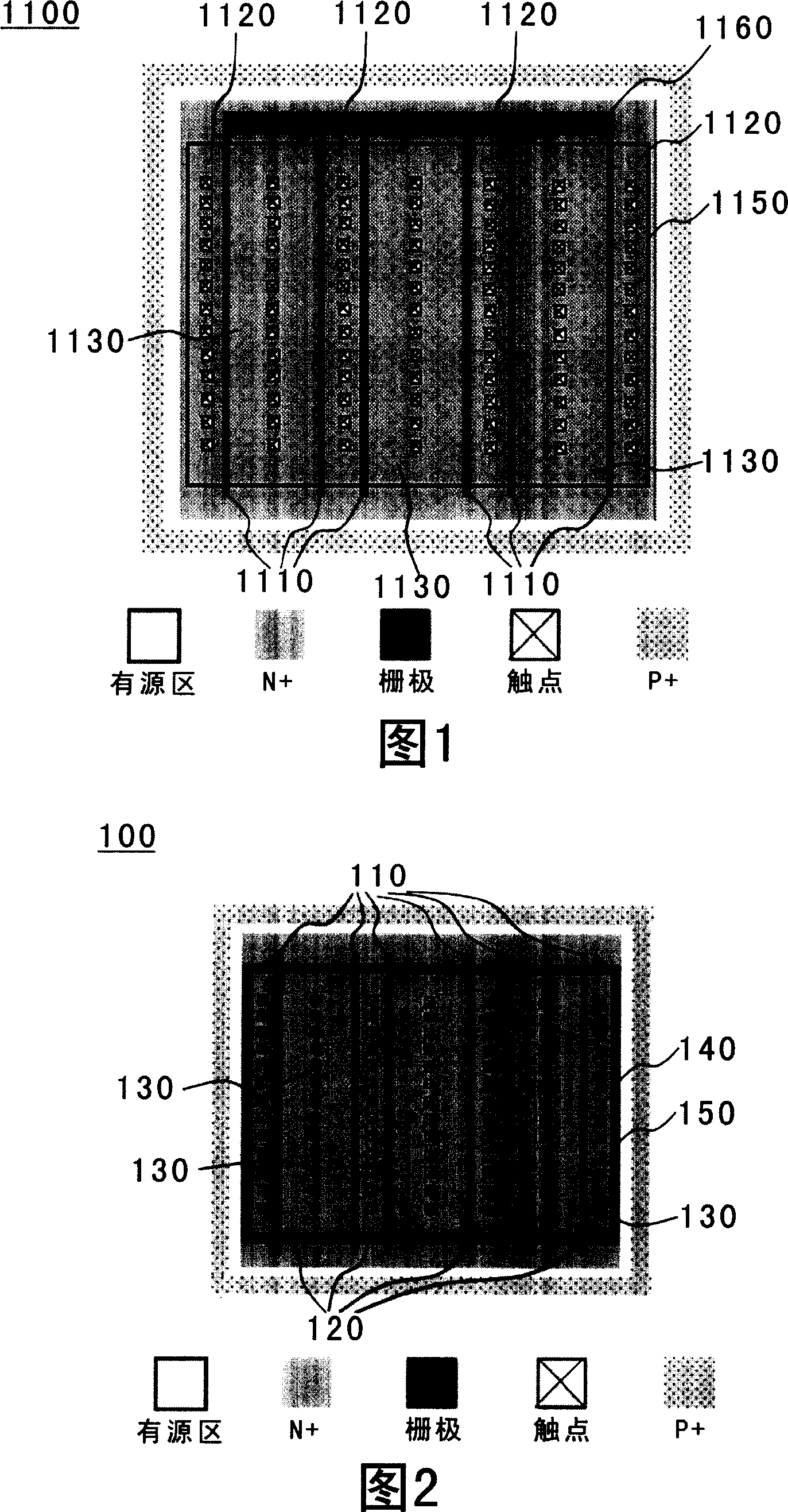

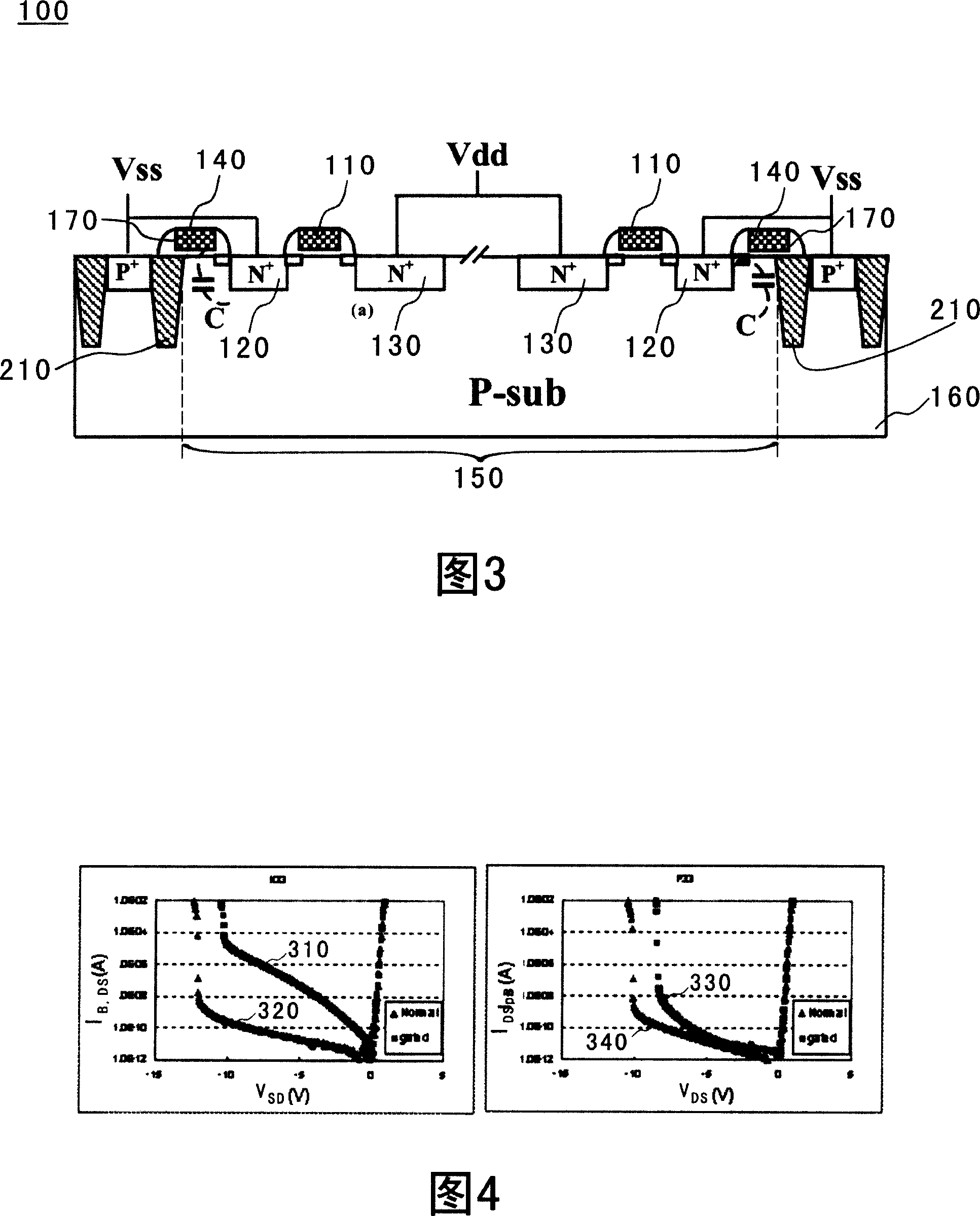

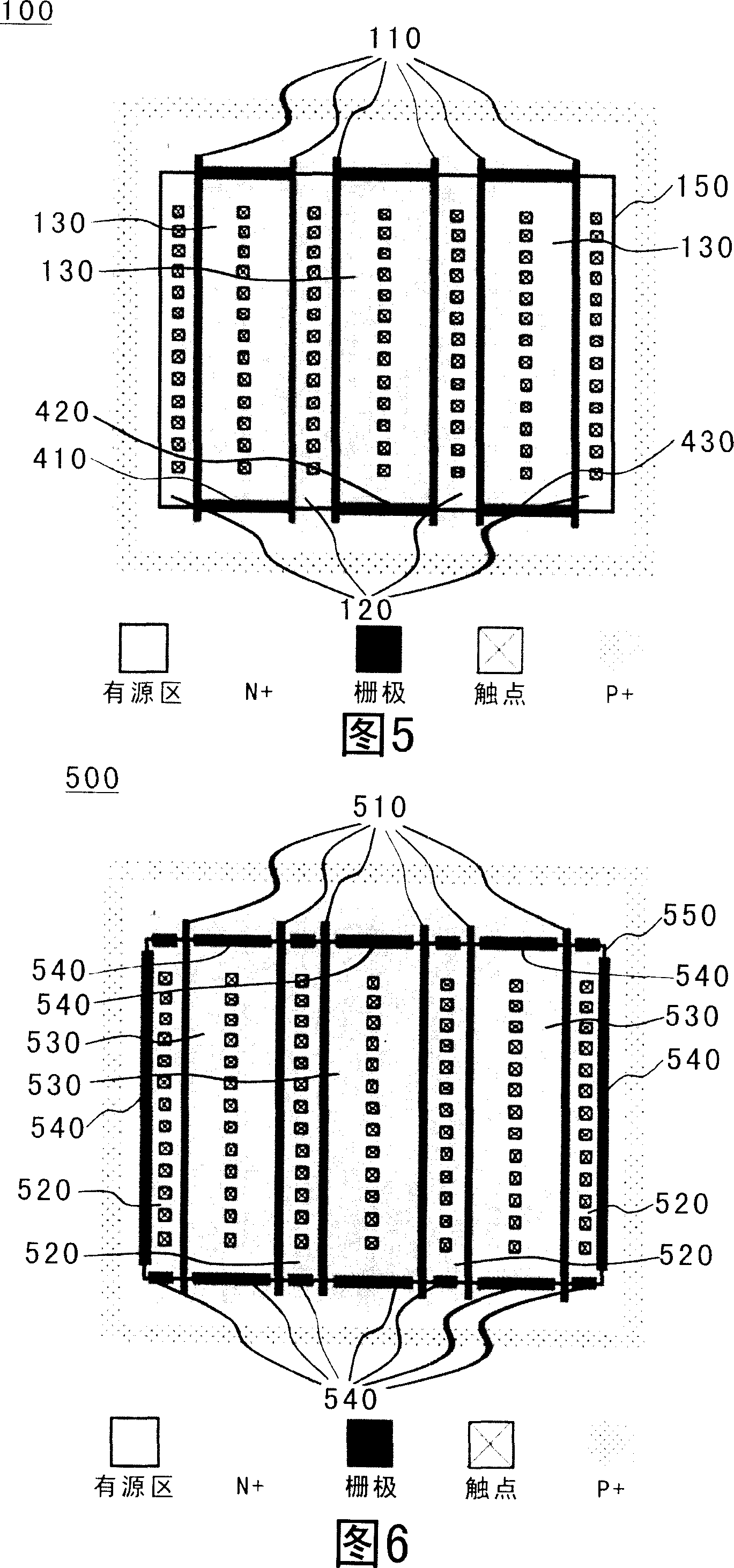

[0023] Figure 1 is a simplified conventional system for ESD protection. System 1100 includes gate region 1110 , source region 1120 , drain region 1130 , active region 1150 and polysilicon region 1160 . Gate region 1110 , source region 1120 and drain region 1130 are used to form I / O transistors in active region 1150 . The gate regions are shorted to each other via the polysilicon region 1160 , which is located entirely outside the active region 1150 . FIG. 2 is a system for electrostatic discharge protection according to an embodiment of the present invention. This diagram is mere...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap