Efficient interrupt system for system on chip design

A technology for managing systems and external equipment, applied in a variety of digital computer combinations, instruments, multi-programming devices, etc., can solve the problems of complexity, increase in integrated circuit time, and inflexibility, and achieve the effect of improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

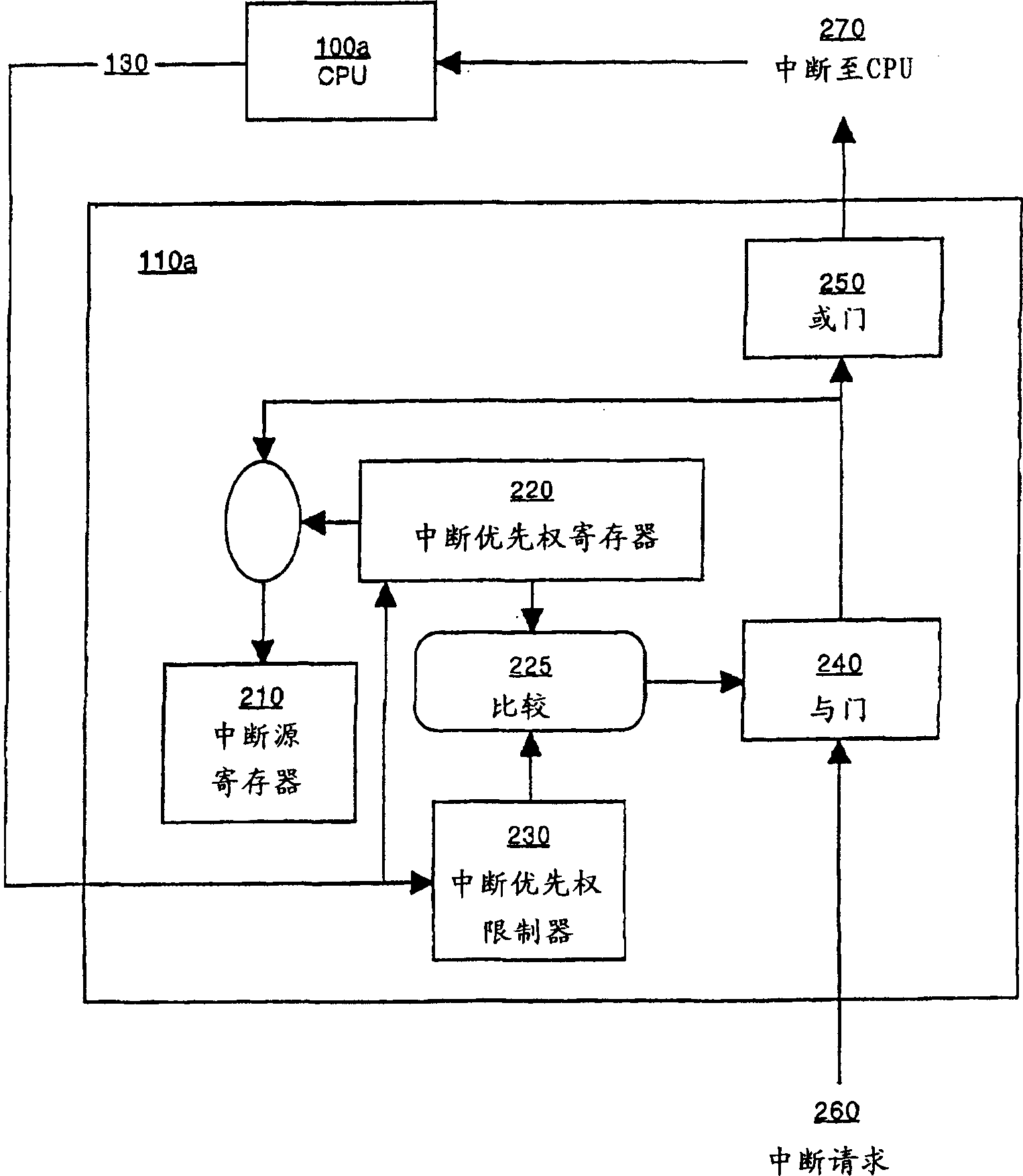

[0018] figure 2 is a block diagram of an embodiment of an interrupt controller according to the present invention.

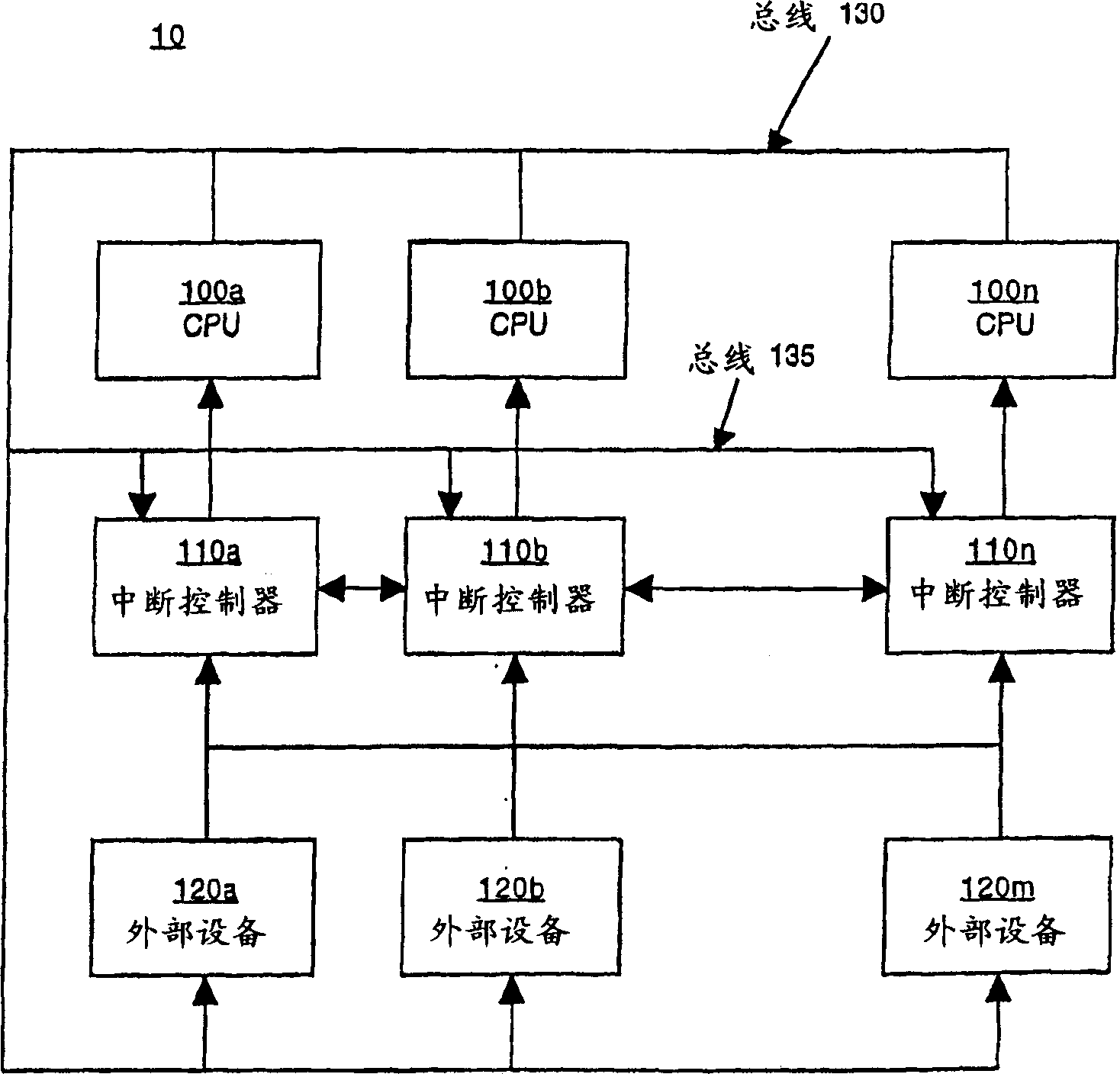

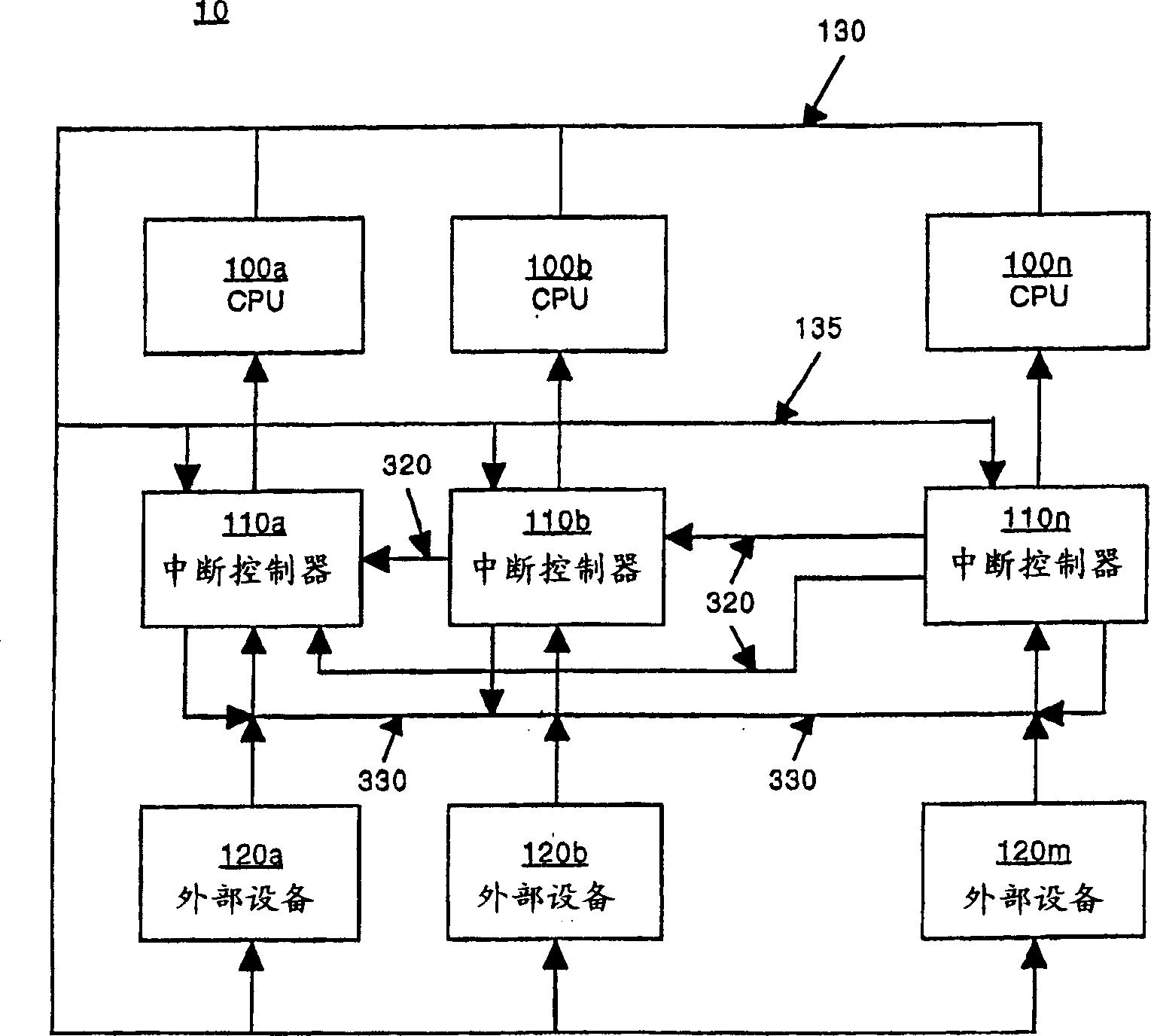

[0019] image 3 yes figure 1 Detailed block diagram of the interconnection between the blocks in the shown interrupt management system.

[0020] Figure 4 It is a flow chart of the steps of the interrupt management process given according to an embodiment of the present invention.

[0021] Figure 5A is a data flow diagram showing inter-processor communication through an interrupt controller according to an embodiment of the present invention.

[0022] Figure 5B is like Figure 5A Timing diagram of interprocessor communication shown.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com