Multichannel ADC system synchronous sampling device and method

A synchronous sampling and multi-channel technology, which is applied in the field of multi-channel ADC, can solve the problem that single chips cannot be aligned with each other, and achieve the effect of data synchronization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

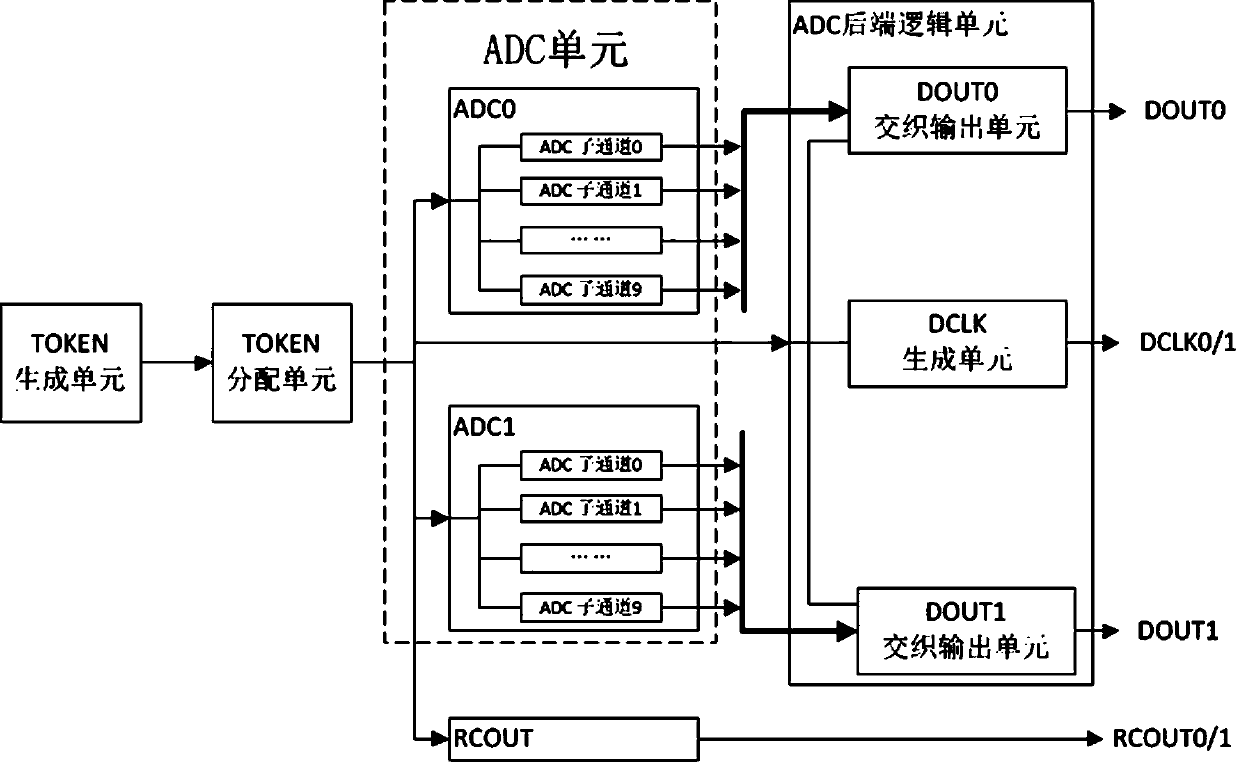

[0046] The present invention designs a device for synchronous sampling of a multi-channel ADC system, which can realize data alignment of multi-channels in the chip, such as figure 1 As shown, the following configuration structure is particularly adopted: a TOKEN generation unit, a TOKEN distribution unit, an ADC unit, an ADC back-end logic unit and RCOUT are provided,

[0047] The TOKEN generation unit generates a cycle factor (TOKEN) based on the sampling clock (CLK);

[0048] The TOKEN allocation unit is used to allocate the cycle factor (TOKEN) to the ADC unit and the ADC back-end logic unit;

[0049] The ADC unit is used to sample the analog input of the corresponding channel and quantize it into a multi-bit digital signal;

[0050] The ADC back-end logic unit is used to generate aligned data clocks and realize the data interleaving output function of the small channels inside the large channel;

[0051] RCOUT is used to transmit the cycle factor to the downstream ADC c...

Embodiment 2

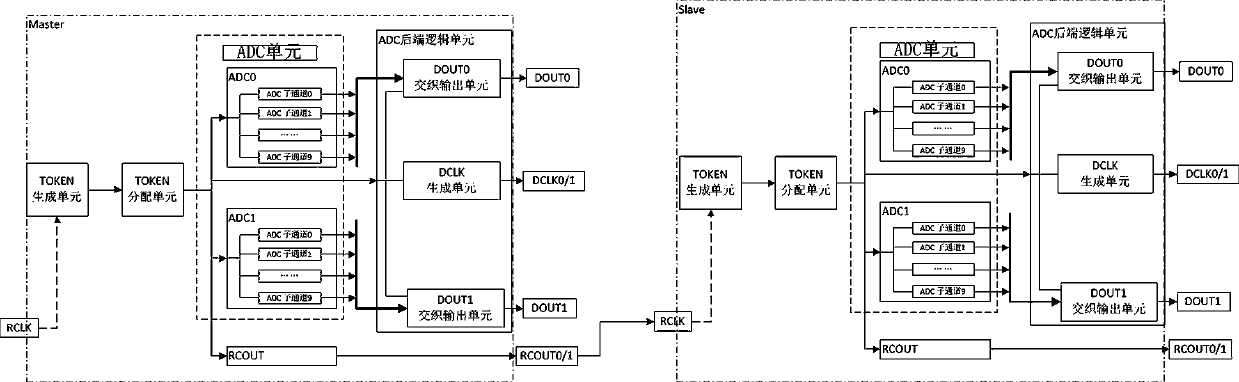

[0056] This embodiment is further optimized on the basis of the above-mentioned embodiments, and the similarities with the technical solutions of the foregoing embodiments will not be repeated here, such as figure 1 As shown, further in order to better realize the synchronous sampling device of the multi-channel ADC system of the present invention, the following setting method is adopted in particular: the TOKEN generation unit works in Master mode or Slave mode.

Embodiment 3

[0058] This embodiment is further optimized on the basis of any of the above-mentioned embodiments, and the similarities with the technical solutions of the foregoing embodiments will not be repeated here, such as figure 1 As shown, further in order to better realize the device for synchronous sampling of the multi-channel ADC system described in the present invention, the following setting method is adopted in particular: In the Master mode, the TOKEN generation unit performs a cycle based on the sampling clock (CLK) Counting, the cycle period is the number N of sub-channels (ADC sub-channels) in the large channel (large-channel ADC), and the counting method uses Gray code; it is used to generate a series of cyclic pulses, and its duty ratio is 1 / N.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com