Programming test device for programmable chip

A test device and chip technology, applied in software testing/debugging, error detection/correction, instruments, etc., can solve problems such as high complexity, low efficiency, and impact on chip life, so as to reduce erroneous operations, improve programming efficiency, and protect The effect of perfect mechanism

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

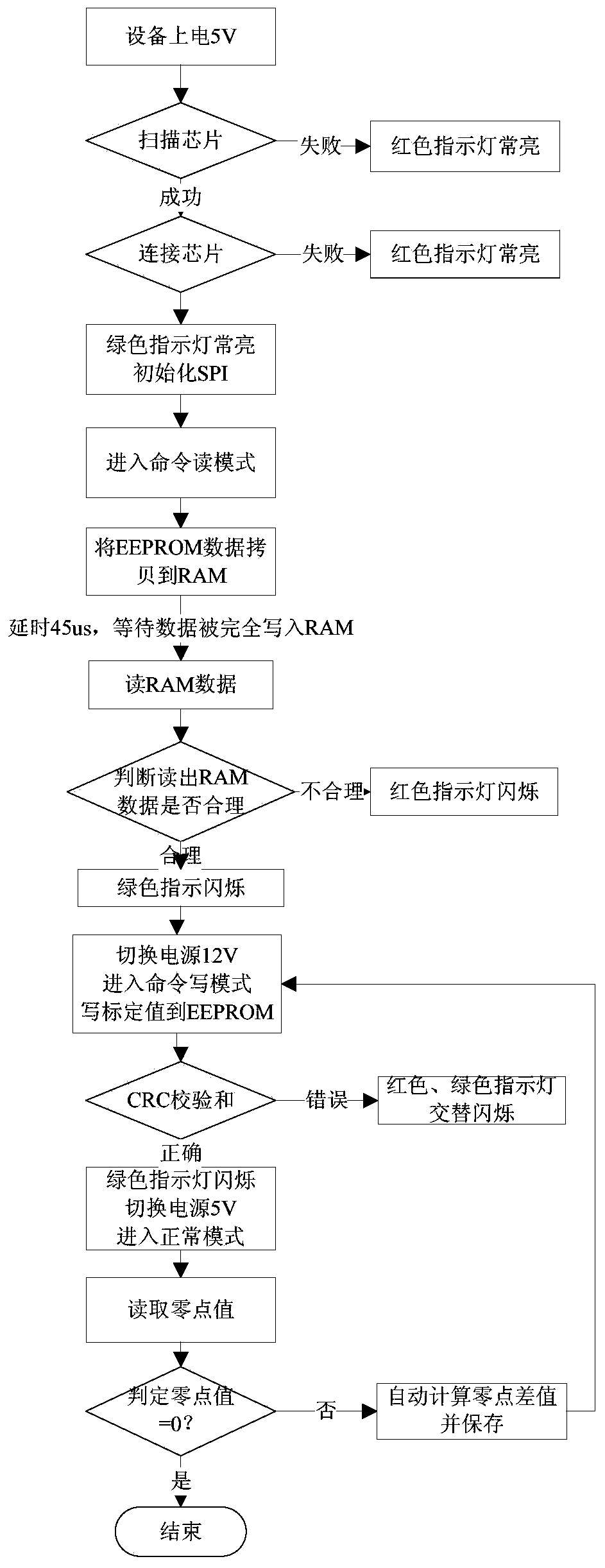

[0026] Below, the present invention will be further described in conjunction with the accompanying drawings and specific embodiments, the content of which is sufficient to enable any person skilled in the art to understand the technical content of the present invention and implement it accordingly, and according to the claims, description and accompanying drawings disclosed in the present invention , those skilled in the art can easily understand the related objects and advantages of the present invention.

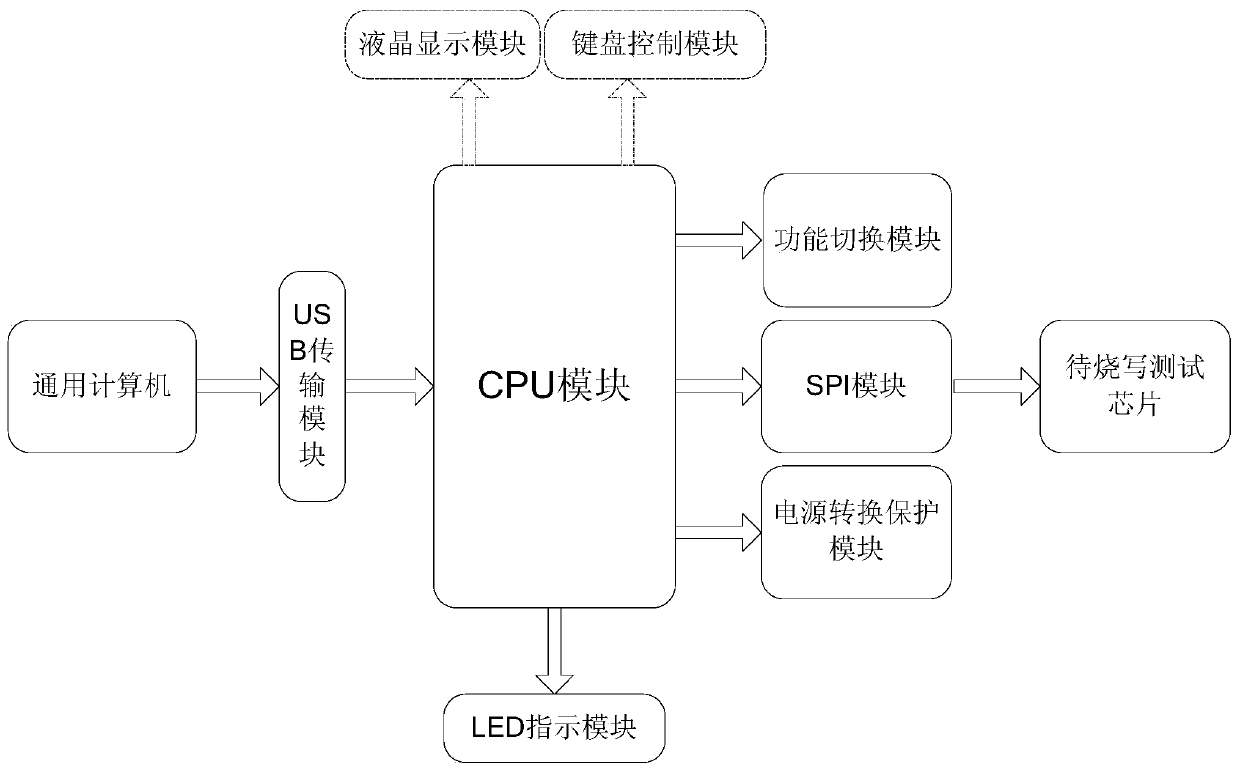

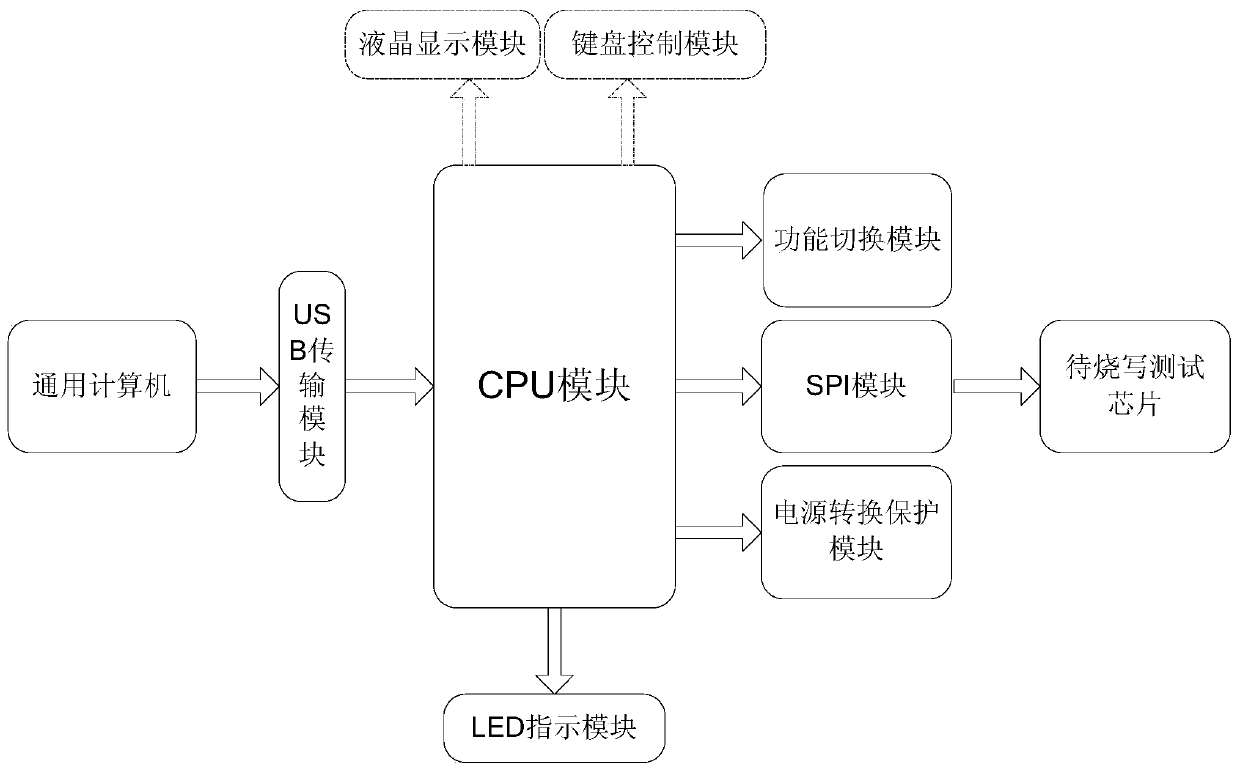

[0027] figure 1 It is a module schematic diagram of a programming test device for a programmable chip of the present invention, which includes a CPU module, an SPI module, a function switching module, a power conversion protection module, an LED indicator module, a liquid crystal display module, a keyboard control module, a USB transmission module, and a module to be burned. Write test chips, etc.

[0028] The CPU module is implemented by STM32F407VGT6 single-chip microco...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com