Packaging structure for rewiring after double-sided bump chip packaging and manufacturing method thereof

A technology of packaging structure and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problems of the overall size of the package, the limitation of the top chip, and the flip position of the top chip cannot exceed the bottom chip, etc. Achieve the effect of improving quality, shortening path, chip size and flexible I/O location

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

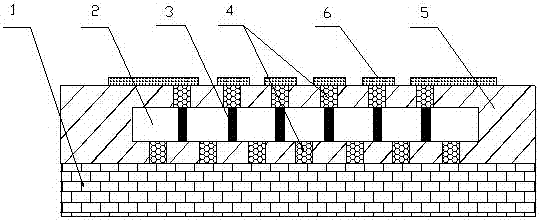

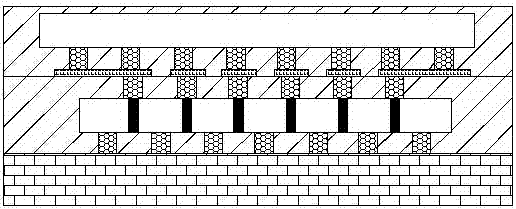

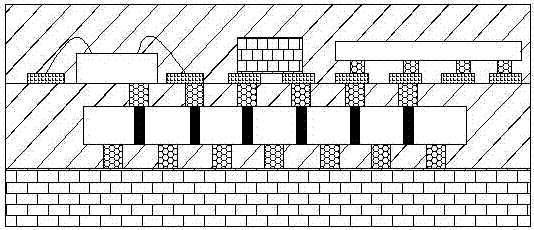

[0044] see figure 1 , the present invention relates to a double-sided BUMP chip encapsulation and rewiring package structure, which includes a substrate 1 and a chip 2, on which a plurality of through-holes 3 are processed by a through-silicon via (TSV) process, and on the chip 2 Metal bumps (BUMP) 4 are provided on the front and back of the chip, and the chip 2 is welded to the front of the substrate 1 through the bumps 4 on the front, and the chip 2 and the bumps 4 on the front and back of the chip 2 are encapsulated with A molding compound 5, the front of the molding compound 5 is flush with the top of the bump 4 on the back of the chip 2, and a metal circuit layer 6 is arranged on the front of the molding compound 5, and the metal circuit layer 6 is connected to the bump 4 on the back of the chip 2. Block 4 is connected.

[0045] The metal circuit layer 6 implements rewiring after encapsulation, and provides electrical connections for subsequent chips and components.

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com