Layout method for PCB (Printed Circuit Board) mounted with BGA (Ball Grid Array) chip and PCB prepared by applying same

A chip and mounting technology, applied in the field of electronic circuits, can solve the problems of increasing the difficulty of PCB layout layout and wiring, increasing the development cycle and production cycle of electronic equipment, and large distribution density, so as to shorten the development and processing cycle, and shorten the development and production time , the effect of reducing difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] Below in conjunction with accompanying drawing and embodiment, further elaborate the present invention.

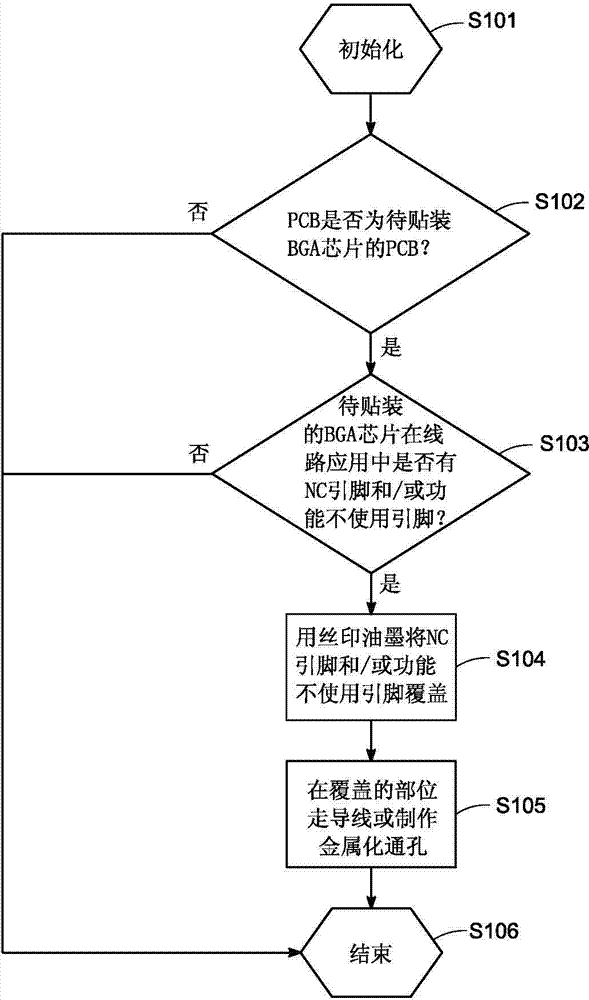

[0023] A PCB layout method with a BGA chip mounted thereon, comprising the following steps:

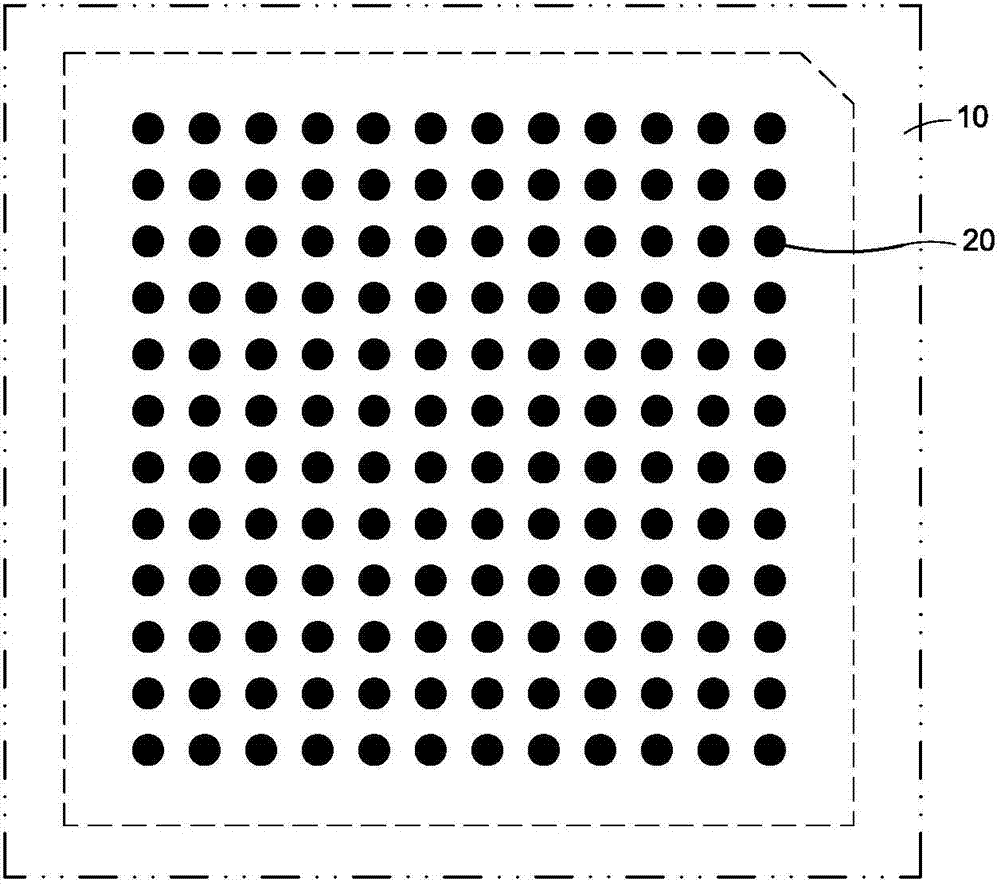

[0024] S1. Provide a PCB to be mounted with a BGA chip, the PCB is provided with solder joints corresponding to the pins of the BGA chip;

[0025] S2. Confirming that the NC pins of the BGA chip and / or function unused pins correspond to the positions of the solder joints on the PCB;

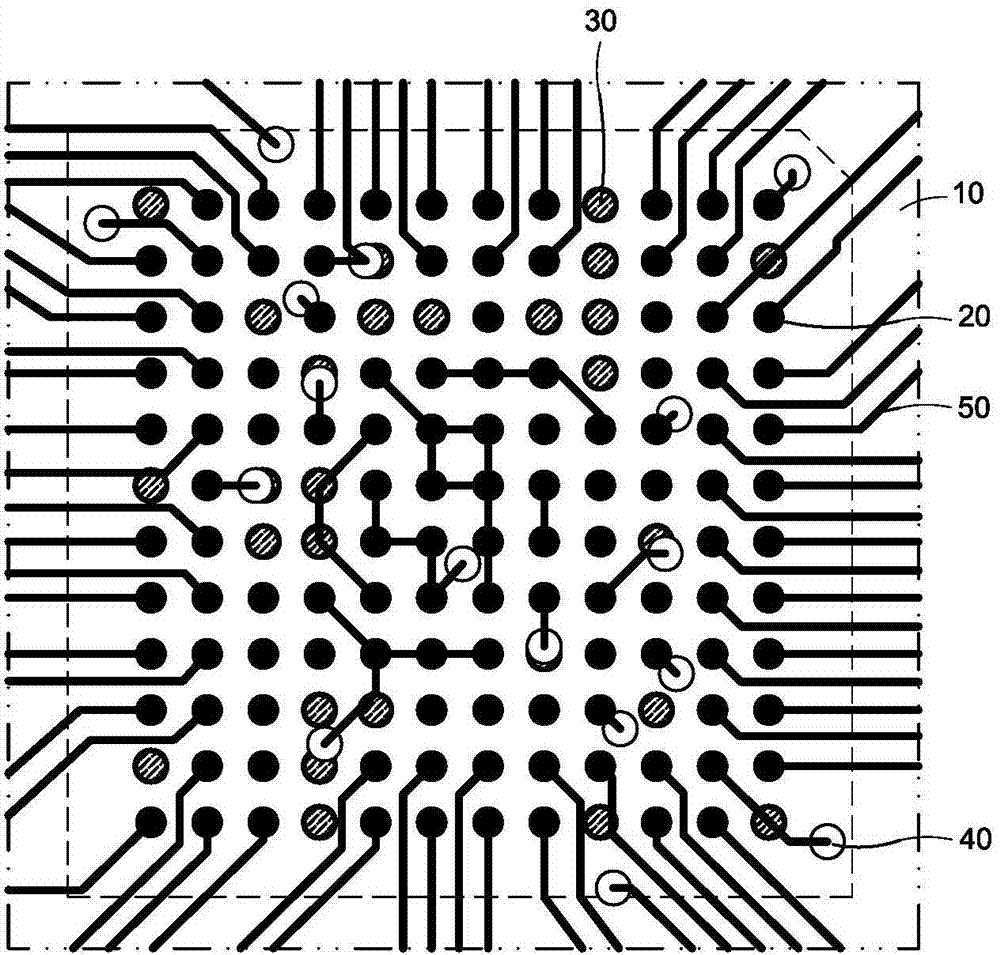

[0026] S3. Cover the solder joints corresponding to the NC pins of the BGA chip and / or functional unused pins with insulating ink;

[0027] S4. Arranging wires or making metallized through holes in the insulating ink coverage area according to functional requirements.

[0028] The specific program flow of the above method is as follows: image 3 Shown:

[0029] The program starts at step S101, performs device initialization at step S101, and enters step S102 after device initialization is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com