Loop-back detecting and inhibiting method of Ethernet exchanger chip port

A switch chip, loopback detection technology, applied in the field of data communication

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

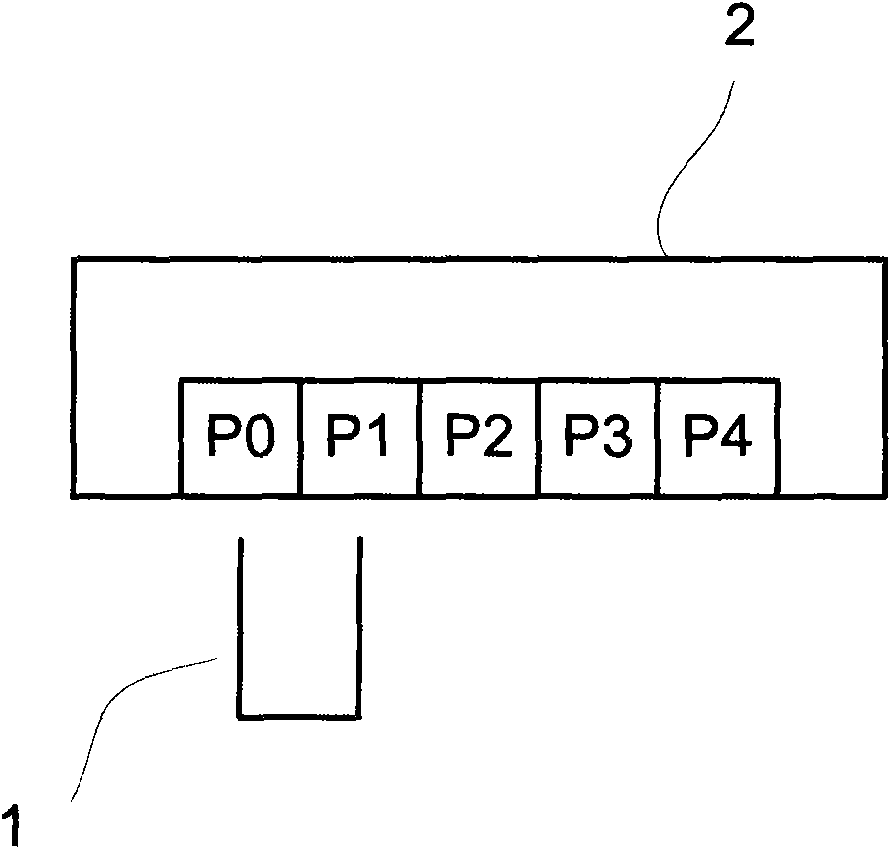

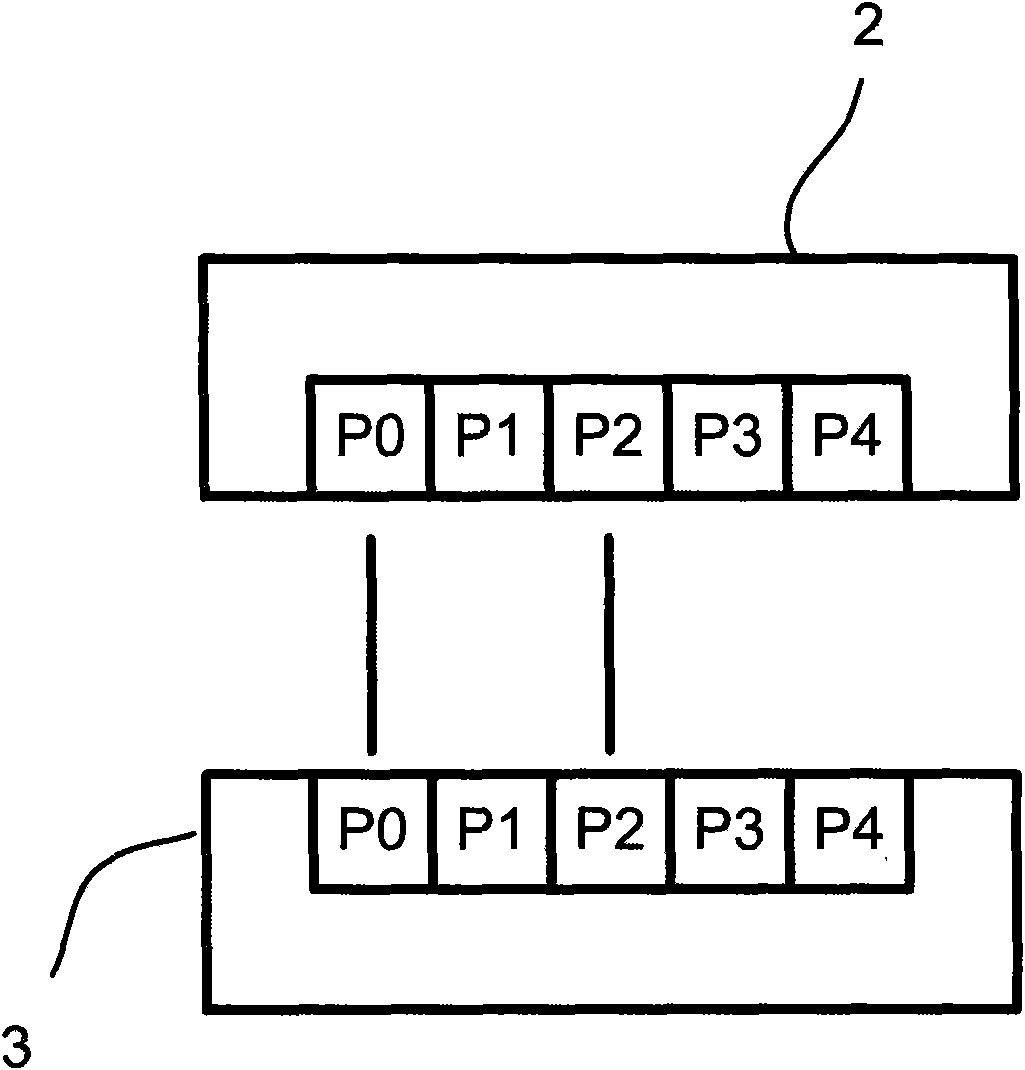

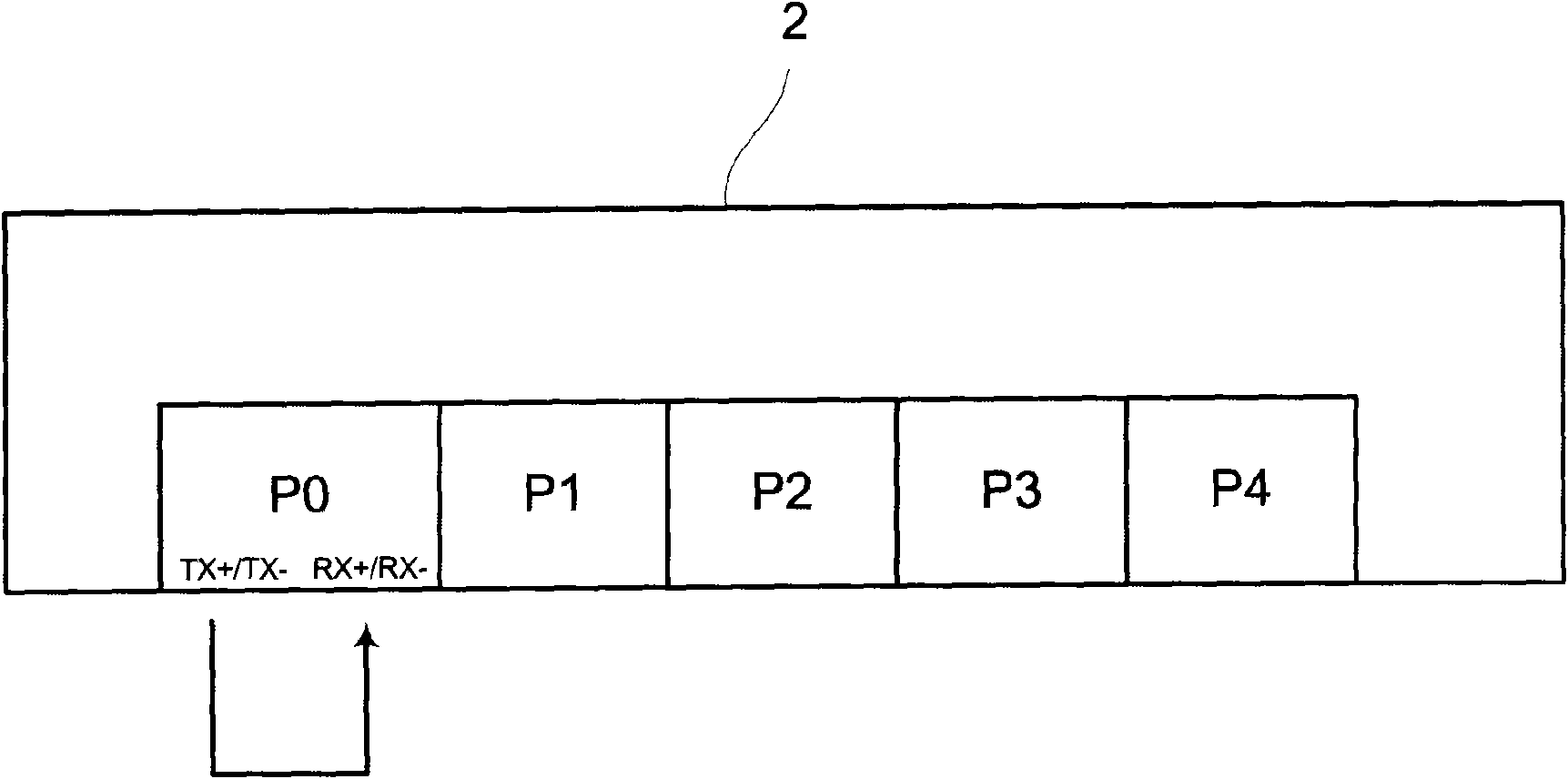

[0013] The loopback detection circuit 7 in the present invention can be realized by a single-chip microcomputer or a programmable logic device. To illustrate the specific implementation, Figure 5 It is a schematic block diagram of a circuit for implementing the present invention taking a 5-port switch chip as an example. An interface of the loopback detection control circuit 7 is connected to the MII interface of the P4 port of a communication port of the switch chip 9, and can communicate with the MII interface specification, and can send frames to the P4 port of the switch chip 9 and receive frames from the P4 port. At the same time, another interface of the loopback detection circuit 7 is connected to the management interface SMI port of the switch chip 9 for configuring the internal parameters of the switch chip 9 and reading internal parameters. In this embodiment, although the loopback detection control circuit 7 is connected to the P4 port and uses the MII interface to comm...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com