PCB stock layout optimization method considering multiple process constraints

An optimization method and process technology, applied in the field of PCB manufacturing, can solve problems such as huge time and cost, low utilization rate, and reduced production adjustments

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] The technical solutions of the present invention will be further described below in conjunction with the accompanying drawings and through specific implementation methods.

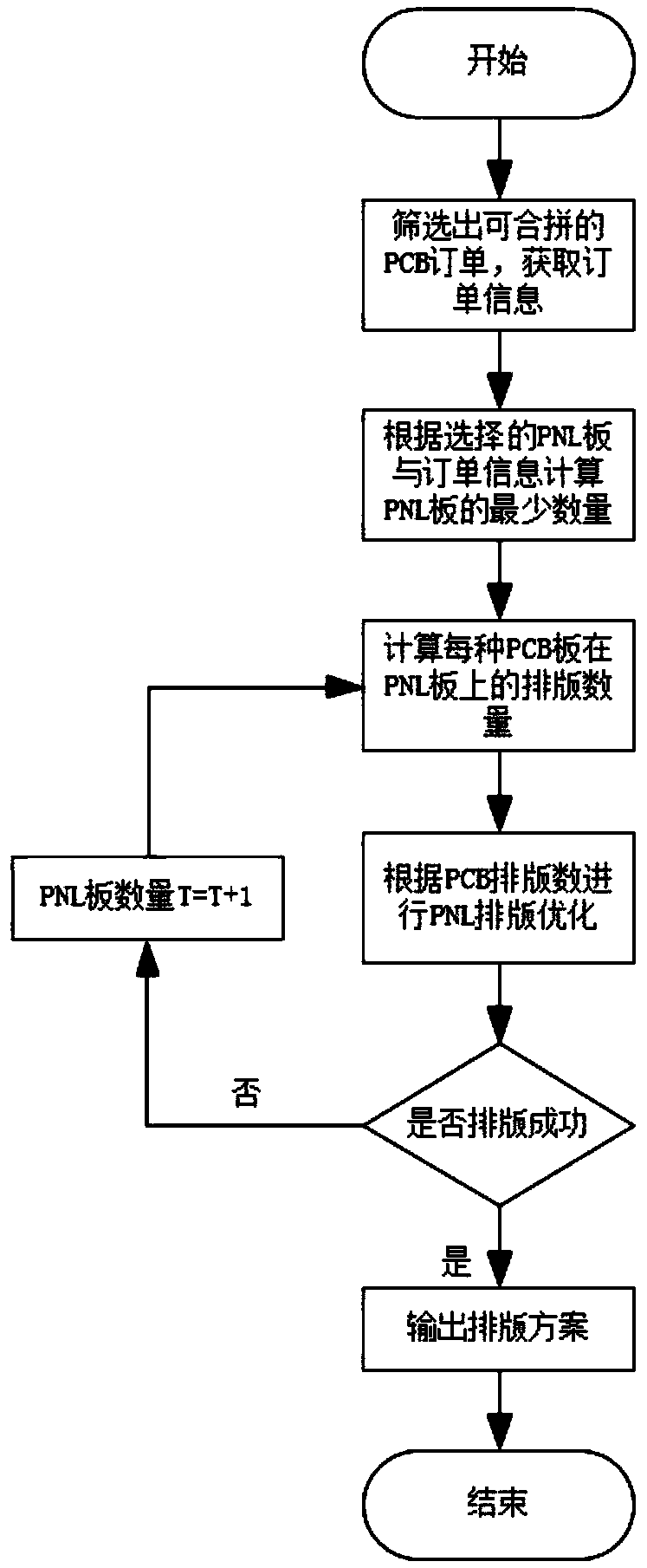

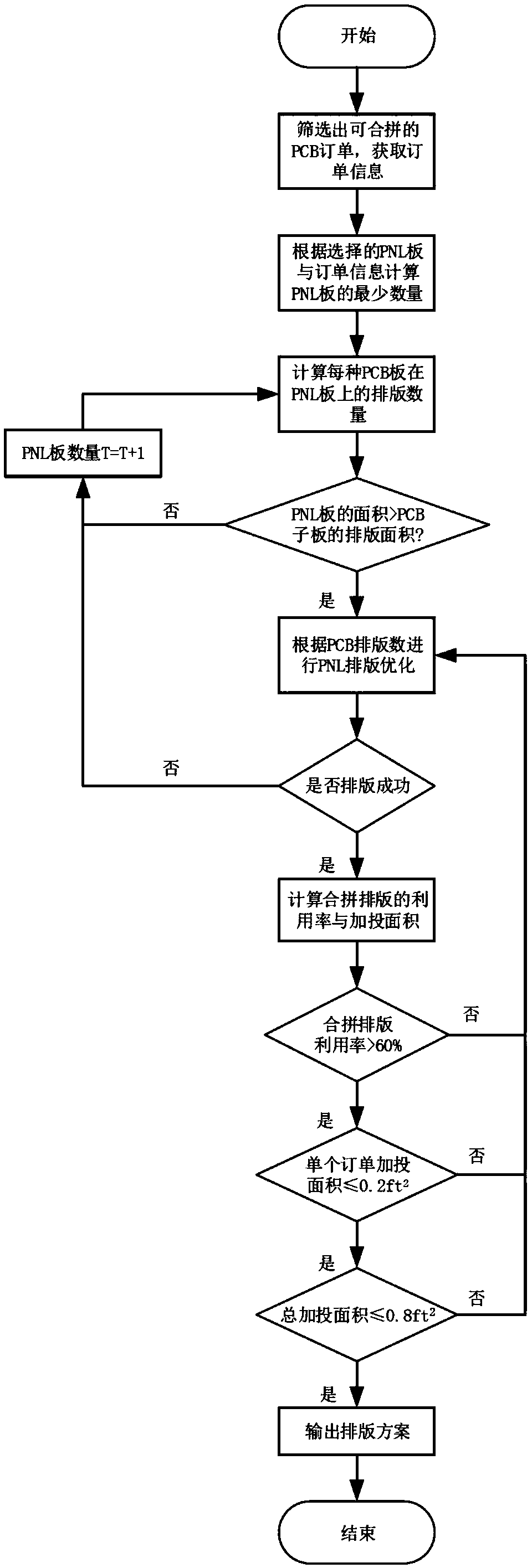

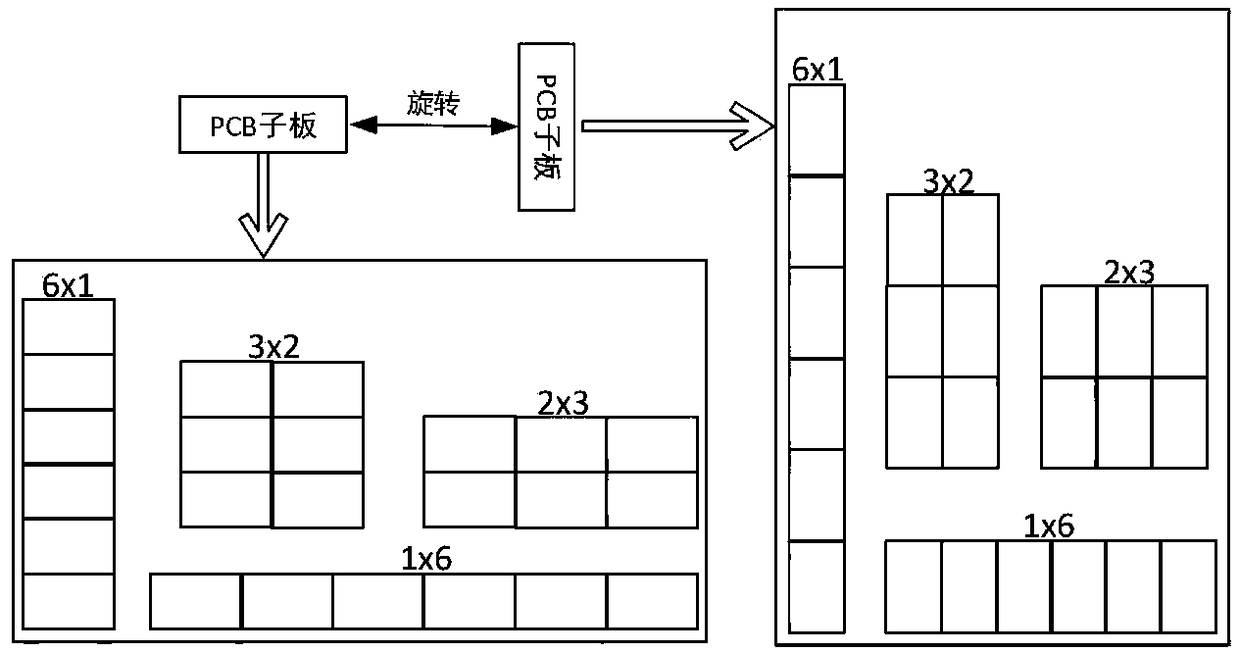

[0052] A PCB layout optimization method considering multiple process constraints in this embodiment is applied to the PCB production management system, such as figure 1 As shown, the following steps are included: Step A: Screen according to the constraint process of the PCB sub-board, and obtain the order information of n kinds of PCB sub-boards that can be assembled, and the order information includes the length l of the PCB sub-board i , width w i , delivery quantity Q i and process constraint information; step B: select a PNL plate in the PNL original film library, and then calculate the minimum required quantity T of PNL plates according to the selected PNL plate and the order information; step C: calculate each PNL plate The number of layouts required for each type of PCB sub-board P i ; Ste...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com