Design method of static random access memory suitable for low-power chip

A static random and design method technology, applied in static memory, digital memory information, information storage, etc., can solve the problems of rare circuit design methods, large load capacitance, large power consumption, etc., and reduce the charging and discharging power of word lines power consumption, improve stability, and reduce gate current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

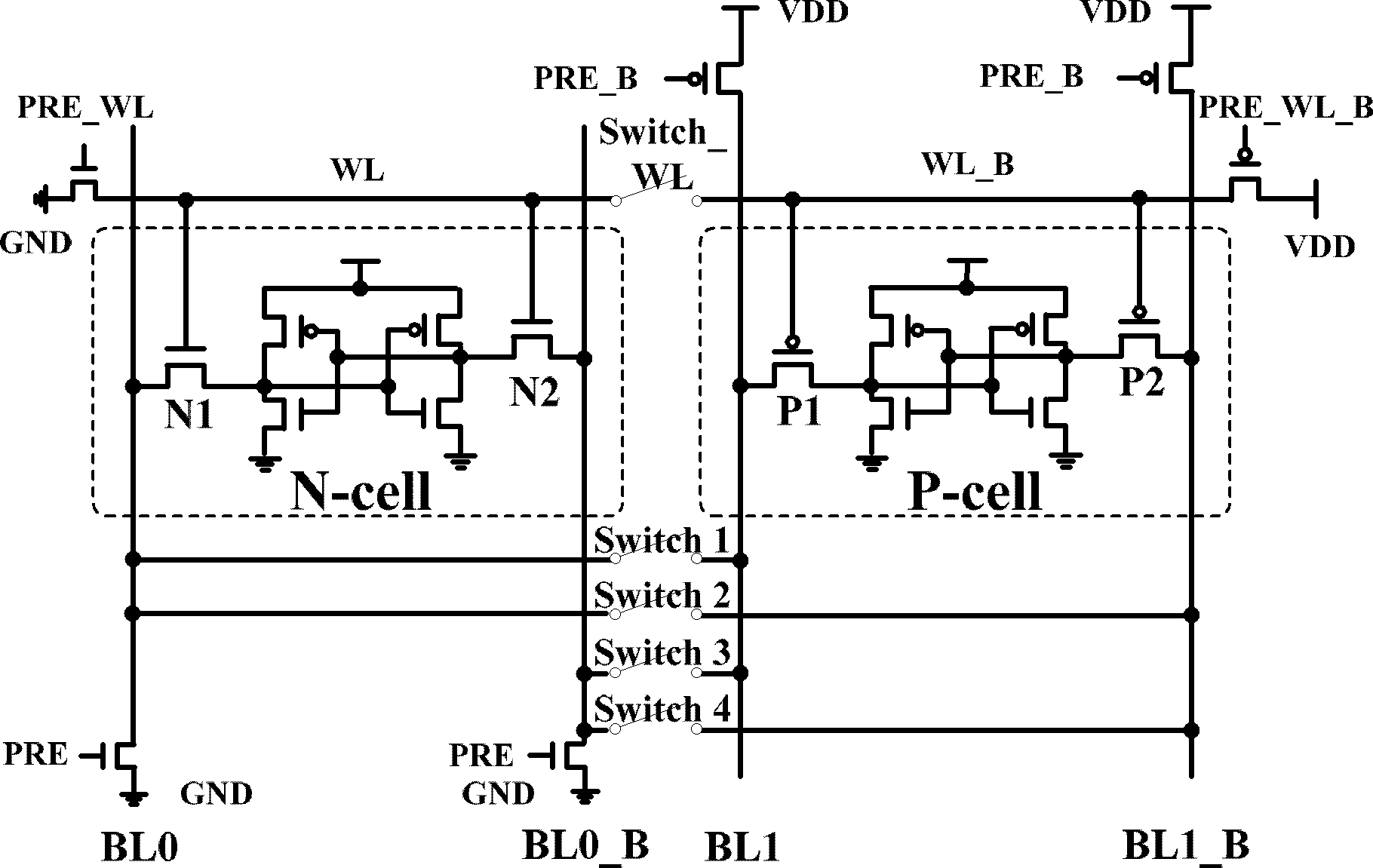

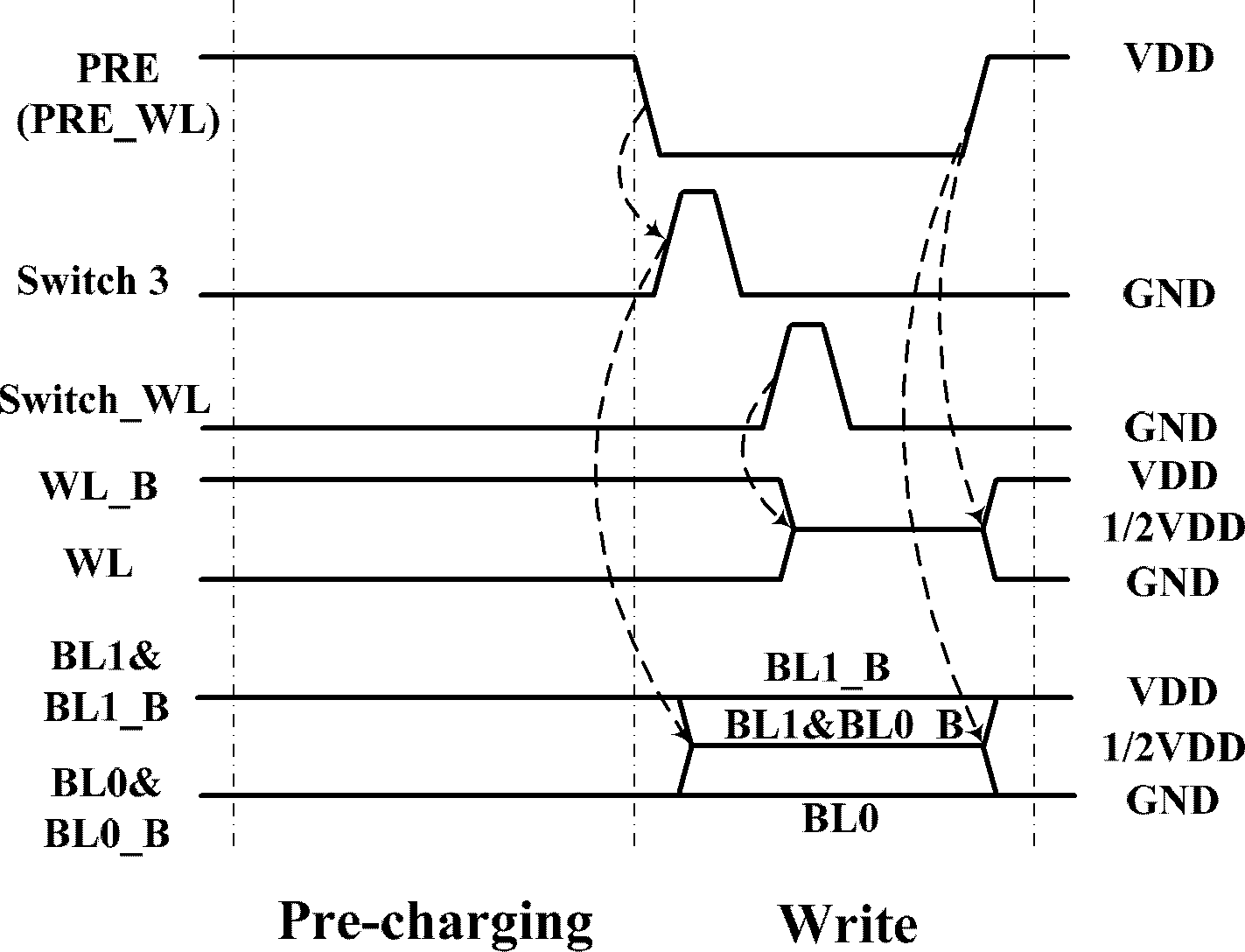

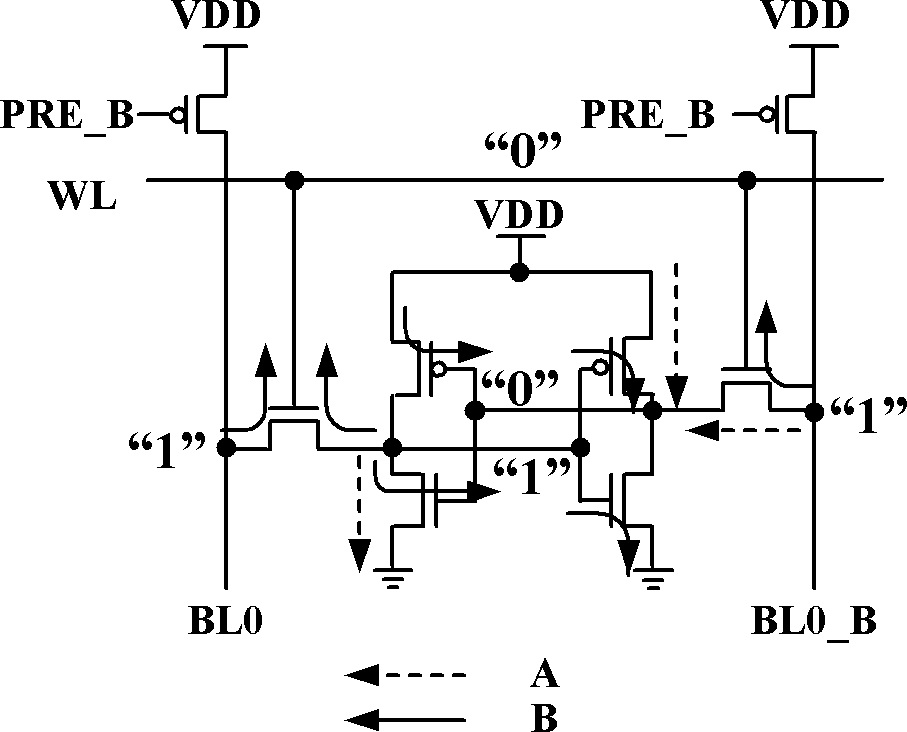

[0036] SRAM of the present invention is a circuit schematic diagram of a group of cell units composed of two different cells, such as figure 1shown. The bit lines BL0 and BL0_B are connected to GND through switches, and the bit lines BL1 and BL1_B are connected to VDD through switches. Four switches Switch1, Switch2, Switch3, and Switch4 control the connection between the bit lines, so that one bit line in the N-cell (or P-cell) can be connected to any one of the P-cell (or N-cell) Root bit line. For example, BL0 connects to BL1 through Switch1, and connects to BL1_B through Switch2. The data to be written is controlled by Switch1, Switch2, Switch3, and Switch4 to achieve the purpose of controlling the voltage difference of the bit lines, thereby writing the data into the inverter ring.

[0037] In the design of the word line, such as figure 1 shown. The access transistors N1, N2 and P1, P2 in the N-cell and P-cell are respectively controlled by two mutually opposite word...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com