FPGA configuration file update device

A configuration file and microprocessor technology, applied in the field of digital systems, can solve the problems of increasing the normal working time of the system, not being able to meet the convenience and speed of online configuration at the same time, and increasing the burden on the microprocessor/microcontroller, so as to achieve online configuration Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The specific embodiments of the present invention are described below in conjunction with the accompanying drawings, so that those skilled in the art can better understand the present invention. It should be particularly reminded that in the following description, when the detailed description of known functions and designs may dilute the main content of the present invention, these descriptions will be omitted here.

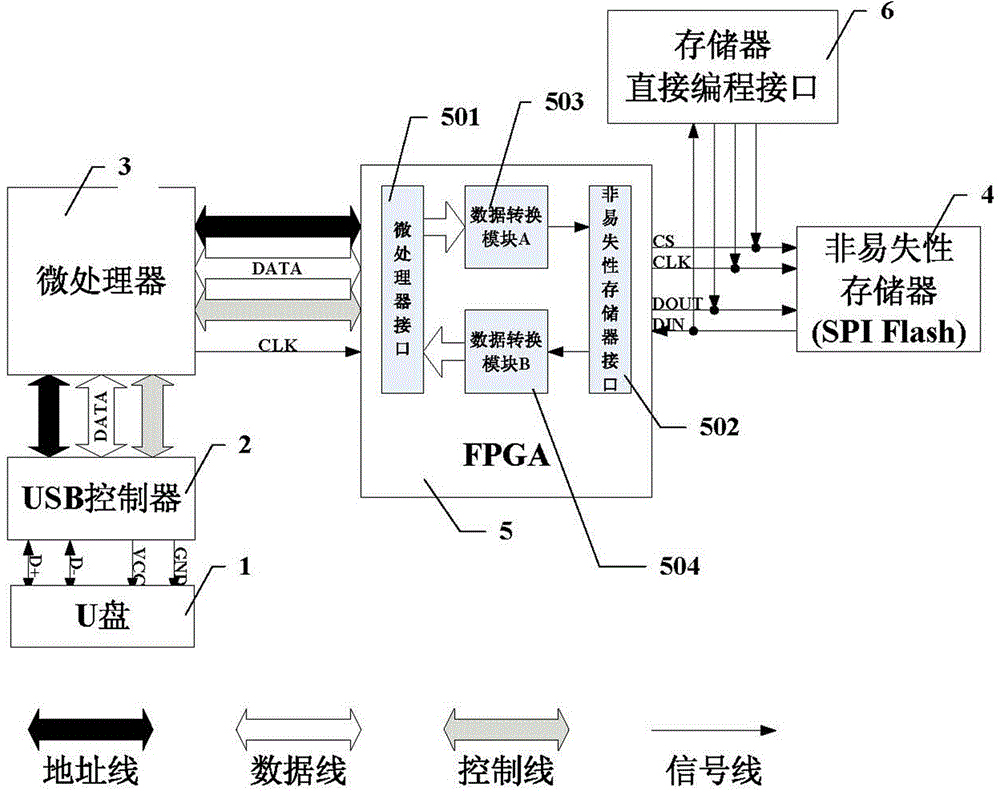

[0021] figure 1 It is a schematic diagram of a specific implementation of the FPGA configuration file update device of the present invention.

[0022] In this embodiment, as figure 1 As shown, the external memory stores FPGA configuration files for the microprocessor / The microcontroller reads. Considering the ease of use and versatility of the operation of updating the FPGA configuration file, the external memory uses a removable disk, which is a U disk in this embodiment 1 , The removable disk has a USB interface, which is versatile, simple and plug and play...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com