155 M bit error code analysis tester based on field programmable gate array

A technology of gate array and tester, which is applied in the direction of digital transmission system, electrical components, transmission system, etc., to achieve the effect of improving reliability and simple circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

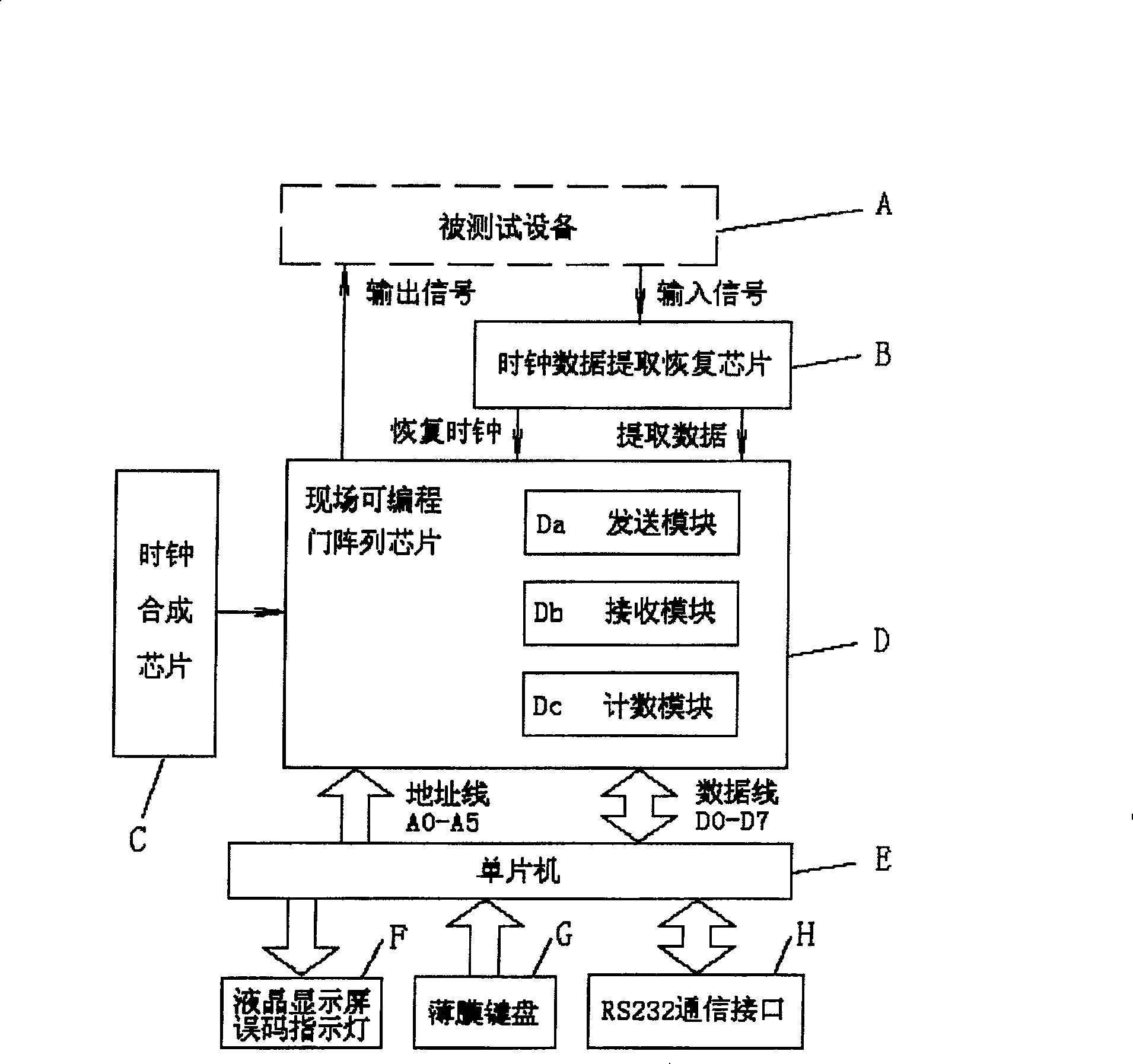

[0071] Further description will be given below in conjunction with the accompanying drawings and embodiments.

[0072] 1. Selection of standard components

[0073] The device under test A refers to the photoelectric conversion module and system-level optical channels and electrical channels;

[0074] Clock data extraction and recovery chip B selects SY87700V;

[0075] Clock synthesis chip C chooses SY87739L;

[0076] SCM E chooses C8051F005;

[0077] The liquid crystal display screen and the error indicator light F use the 20464C of Jingdian Pengyuan;

[0078] Membrane keyboard G uses 3X3 keyboard connection;

[0079] Serial port communication interface H selects MAX3223E chip.

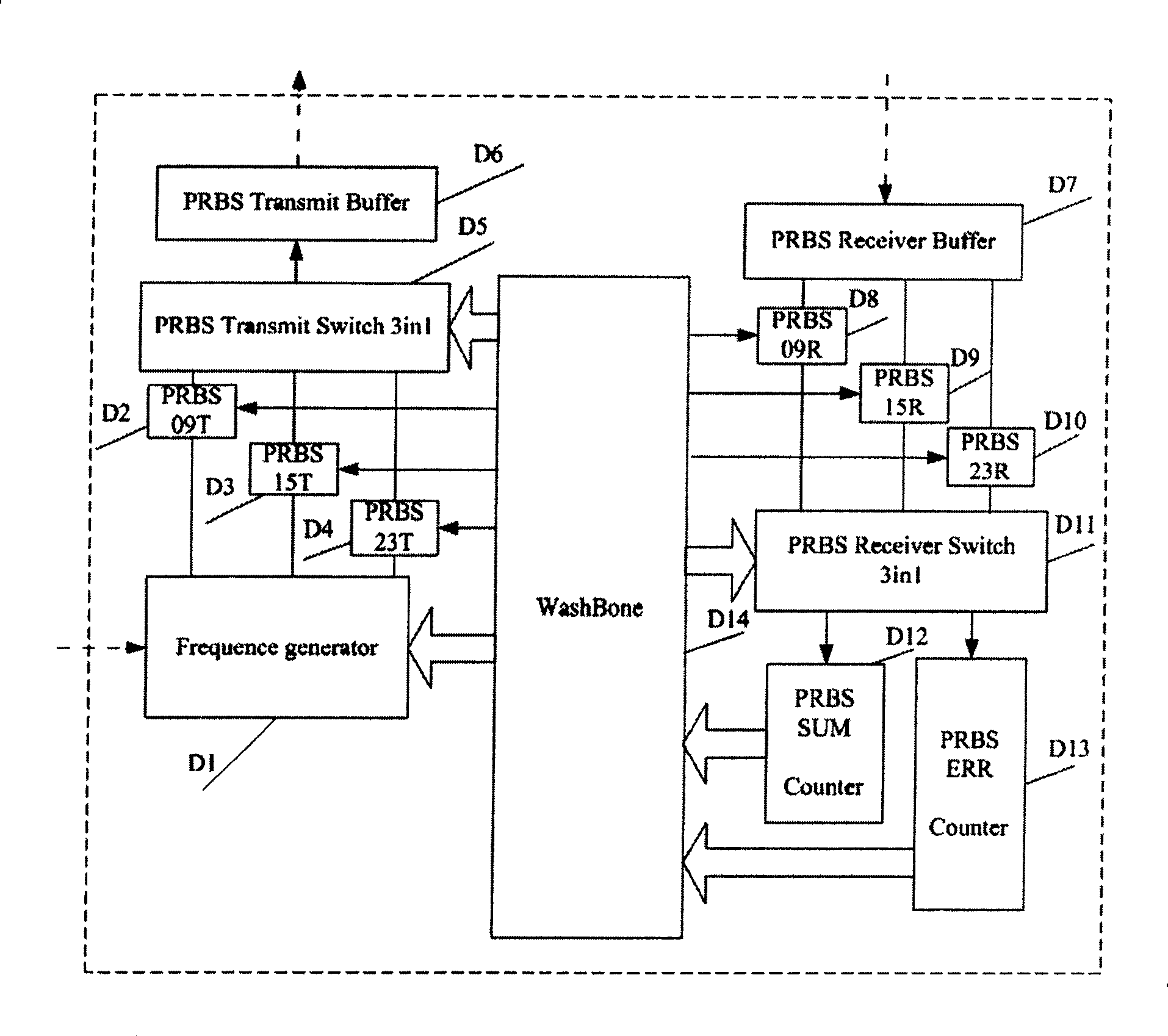

[0080] 2. Implementation of Field Programmable Gate Array Chip

[0081] Considering the working voltage, processing speed, price, supported interface types, capacity and power consumption of equivalent logic gates, the field programmable gate array chip D chooses Xilinx's Spartan IIE series XC2S...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap