CMOS (complementary metal oxide semiconductor) device and production method thereof

A technology of devices and stacked gates, which is applied in the field of CMOS semiconductor device preparation, can solve the problems of increasing the time required for the process, reducing the production efficiency, and failing to achieve compensation, etc., achieving the effects of low process implementation cost, improved device performance, and small process changes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The specific embodiment of the present invention will be further described below in conjunction with accompanying drawing:

[0036] The present invention provides a kind of CMOS device preparation method, can refer to as shown in the figure, specifically comprise the following steps:

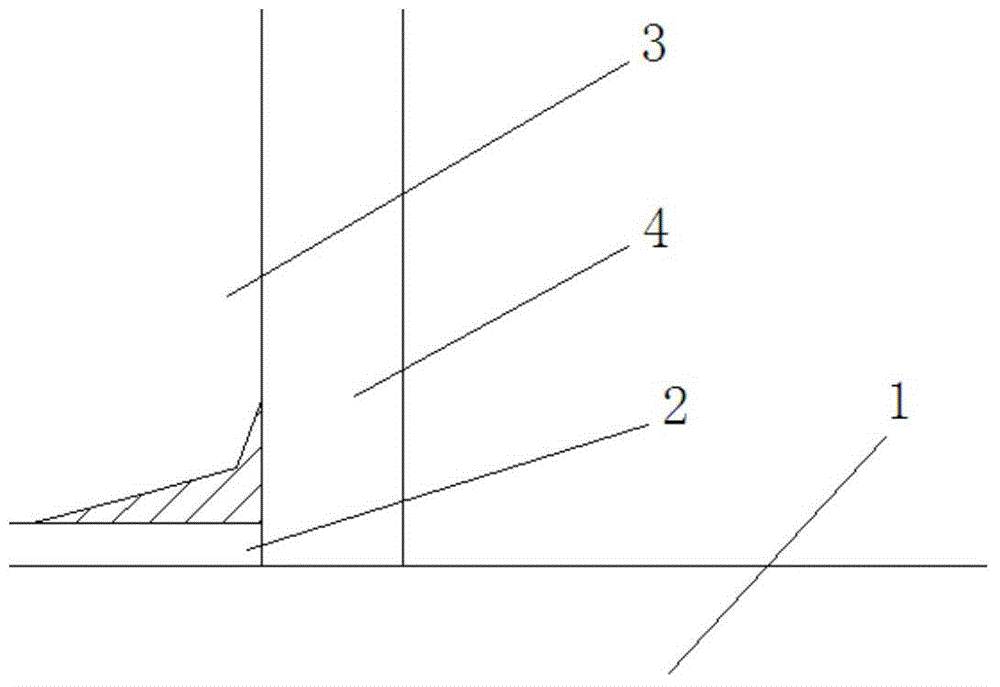

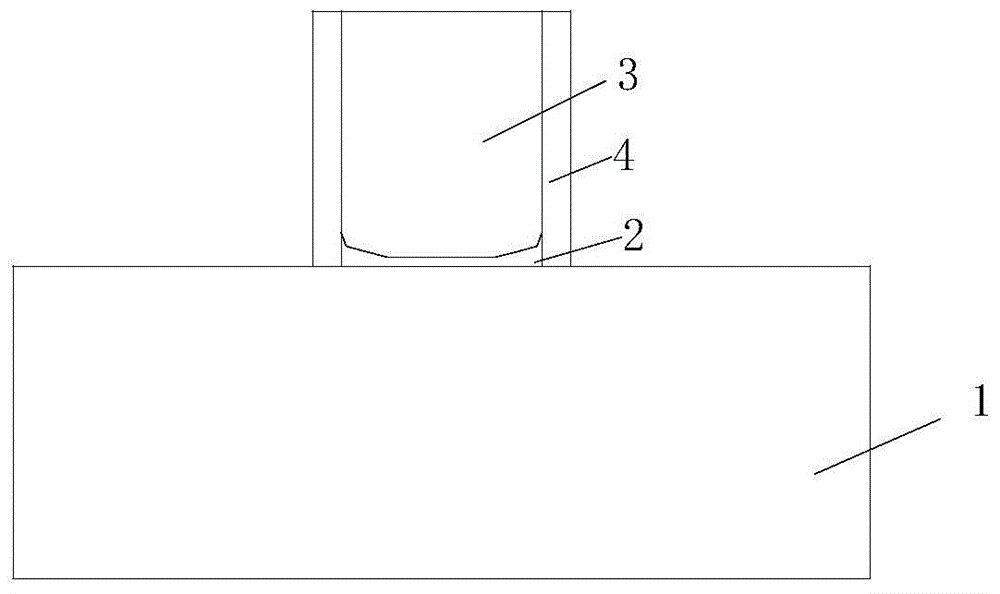

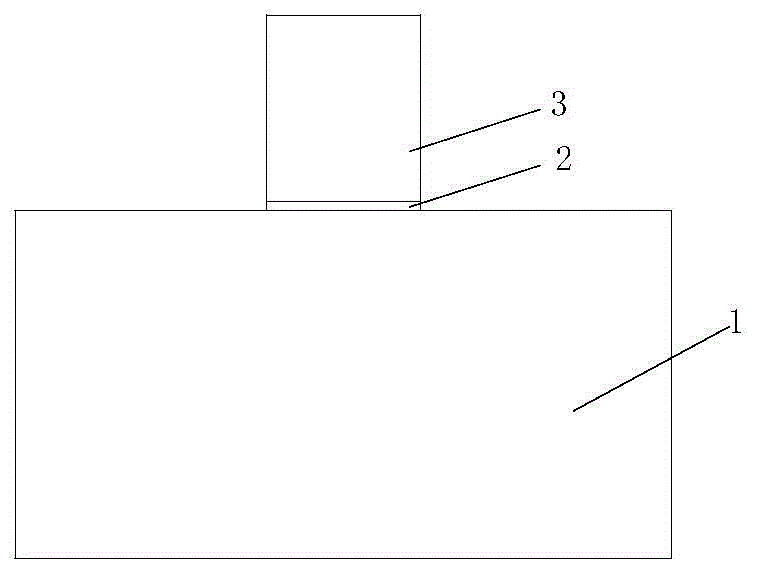

[0037] Step S1: Provide a bottom substrate 1, deposit a layer of gate oxide layer and a polysilicon layer on the substrate in sequence, then spin-coat a layer of photoresist on the surface of the polysilicon layer, and use a mask with a window pattern to expose and The development process forms an opening in the photoresist, and then uses the opening to etch down the polysilicon layer and the gate oxide layer to form a stacked gate; as image 3 As shown, the gate stack includes a gate oxide layer 2 at the bottom and a polysilicon gate 3 located on the gate oxide layer 2. In an embodiment of the present invention, the gate oxide layer is made of silicon dioxide (SiO 2 ).

[0038] Step S2...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com