What is a Half Adder?

A half adder is a basic digital logic circuit that performs addition of two single-bit numbers. It produces a sum bit and a carry bit. The sum bit is the XOR (exclusive OR) of the two input bits, and the carry bit is the AND of the two input bits.

Truth Table of a Half Adder

| Input A | Input B | Sum (S) | Carry (C) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

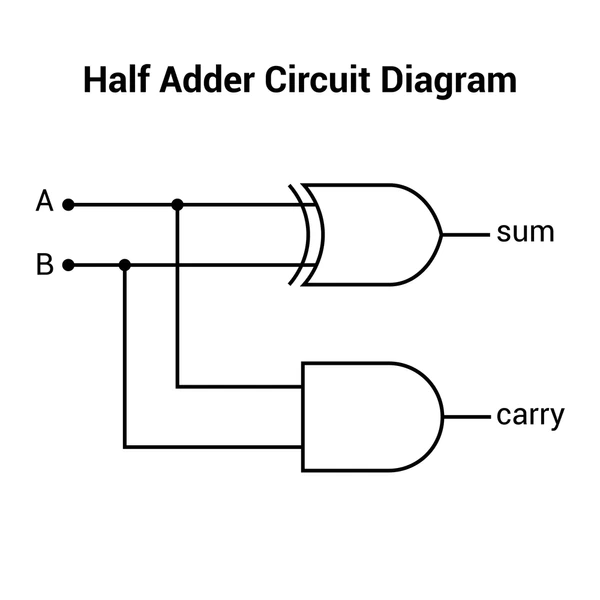

Circuit Diagram of a Half Adder

Types and Variations

- Molecular Beacon-Based Half Adder: Uses DNA-based logic circuits inspired by molecular beacons.

- Optical Binary Half Adder: Utilizes optical components with coherent light sources and operates at high speeds with low power consumption.

- Spin Half-Adder: Uses the circular current and induced magnetic field in a nano-junction to regulate spin alignments for output determination.

- Single-Electron Half-Adder: Represents bits by the presence or absence of single electrons at conducting islands.

- Fluidic Digital Half-Adder: Uses fluid dynamics with water droplets to represent binary signals.

Key Features of a Half Adder

- Binary Addition: It adds two binary input bits and produces two outputs: the sum bit and the carry bit.

- Basic Logic Gates: It can be implemented using two primitive logic gates: an XOR gate for the sum bit and an AND gate for the carry bit.

- Simplicity: It is the simplest form of an adder circuit, making it a fundamental component in digital design.

- Applications: They are used in arithmetic logic units (ALUs) and are essential in the design of more complex adder circuits.

Limitations of a Half Adder

- Limited Capacity: Can only add two bits at a time, requiring multiple half-adders to add larger numbers.

- No Carry-In: Does not consider any carry-in from a previous bit addition, which is necessary for adding larger numbers.

- Sequential Operation: Requires sequential operation to add multiple bits, which can be slow for large numbers.

Comparison with Full Adder

- Functionality:

- Half Adder: Adds two binary input bits and produces a sum bit and a carry bit. It does not consider any carry-in bit.

- Full Adder: Adds a pair of binary input bits and a carry-in bit to produce a sum bit and a carry-out bit.

- Input and Output:

- Half Adder: Two input bits (A and B) and two output bits (sum and carry).

- Full Adder: Three input bits (A, B, and Cin) and two output bits (sum and Cout).

- Carry Management:

- Half Adder: Only handles the carry between two bits.

- Full Adder: Handles the carry between three bits, including a carry-in bit from the previous bit position.

- Circuit Complexity:

- Half Adder: Typically simpler and requires fewer transistors (e.g., 3 transistors in a 3-T Half Adder design).

- Full Adder: More complex and requires more transistors (e.g., 14 transistors in a conventional CMOS full adder).

Advantages

- Half Adders:

- Simplicity: Easier to design and implement due to its simplicity.

- Low Power Consumption: Generally consumes less power compared to a full adder.

- Area Efficiency: Takes up less space on a semiconductor substrate.

- Full Adders:

- Versatility: Can handle more complex addition tasks, including carry-in bits, making it suitable for multi-bit arithmetic operations.

- Performance: Can be optimized for high-speed and low-power consumption in advanced designs.

- Scalability: Can be cascaded to form multi-bit adders, which are essential in digital processors and arithmetic logic units (ALUs).

Applications of Half Adder

- Digital Arithmetic Operations:

- Adders: Half Adders are used to construct full adders, which are crucial for performing addition operations in digital systems. They are integral in the design of arithmetic logic units (ALUs) found in computers and other digital devices.

- Subtractors and Counters: These circuits also find applications in subtractors and counters, which are essential for various digital applications, including timing and counting mechanisms.

- Energy Efficiency in Digital Circuits:

- The integration of simple logic gates like the half-adder into higher-level circuits is important for understanding and optimizing energy efficiency. Studies on half-adders focus on minimizing power loss, which is crucial for the development of energy-efficient digital devices.

- Potential Applications in Molecular Level Devices:

- The principles of half-adders can be applied to molecular level devices, where digital logic is used to control and manipulate molecular processes. This application is still in the realm of research but holds promise for future advancements in nanotechnology and molecular computing.

- Understanding Biological Processes:

- The mechanisms of half-adders can provide insights into complex biological processes. By understanding how simple digital circuits function, researchers can gain a better grasp of the underlying principles of biological systems that perform arithmetic operations.

Latest Technical Innovations in Half Adder

- Power Efficiency Improvements:

- Recent innovations focus on reducing power consumption by selectively turning off parts of the half adder circuitry, which is beneficial for applications in AI chips and other power-sensitive devices.

- Pipelining for Speed Enhancement:

- Pipelining techniques have been developed to enable half adders to perform additions in parallel, thus speeding up the process and improving the performance of ALUs and CPUs.

- Fluidic and Spin-Based Implementations:

- Fluidic half-adders offer a unique approach to digital logic using fluid dynamics, while spin-based half-adders utilize magnetic fields to regulate output states, providing alternative methods for implementing half adders.

- Quantum Dot Applications:

- The use of quantum dots for half adders provides a means for energy-efficient and autonomous operation, which is advantageous in noisy environments.

To get detailed scientific explanations of half adders, try Patsnap Eureka.

Learn more

Multiplexor: Efficient Data Selector for Electronics

Understanding STP Cable: Shielded Twisted Pair Explained

Understanding Twisted Pair Cable: Basics, Benefits, and Uses